主题中讨论的其他部件:UCC2.7201万A,UCC2.7211万A-Q1

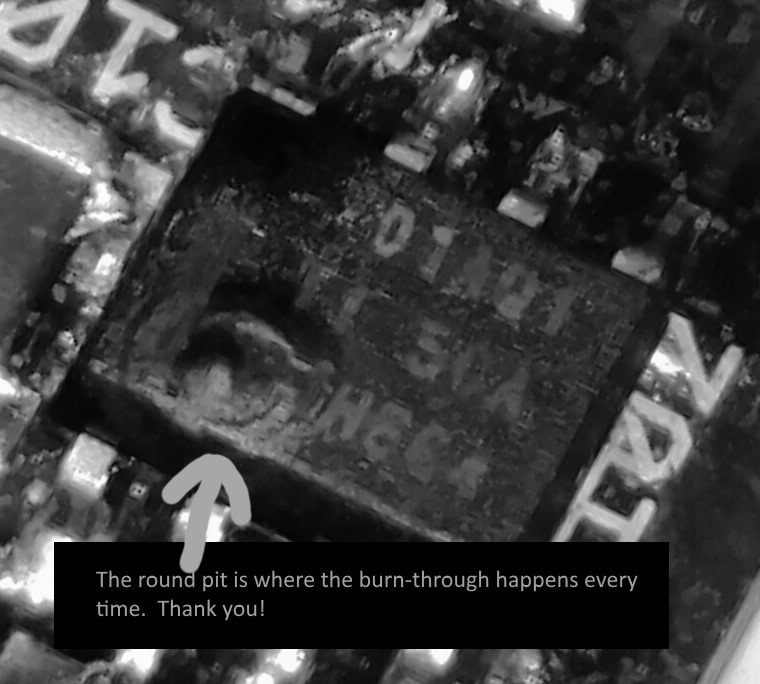

在使用 UCC2.7201万A (和-Q1版本)的新设计中,我们遇到了重复性故障。 故障方法是一致的;芯片上的一个点变为亮红色,并通过顶部烧出一个孔。 我通过几种途径尝试找出导致故障的原因,我希望您能够帮助我根据烧穿的位置来确定问题的重点。 我附上了芯片的图像-我对分辨率表示歉意,但显微镜很忙,我希望这将足以确定大致位置。

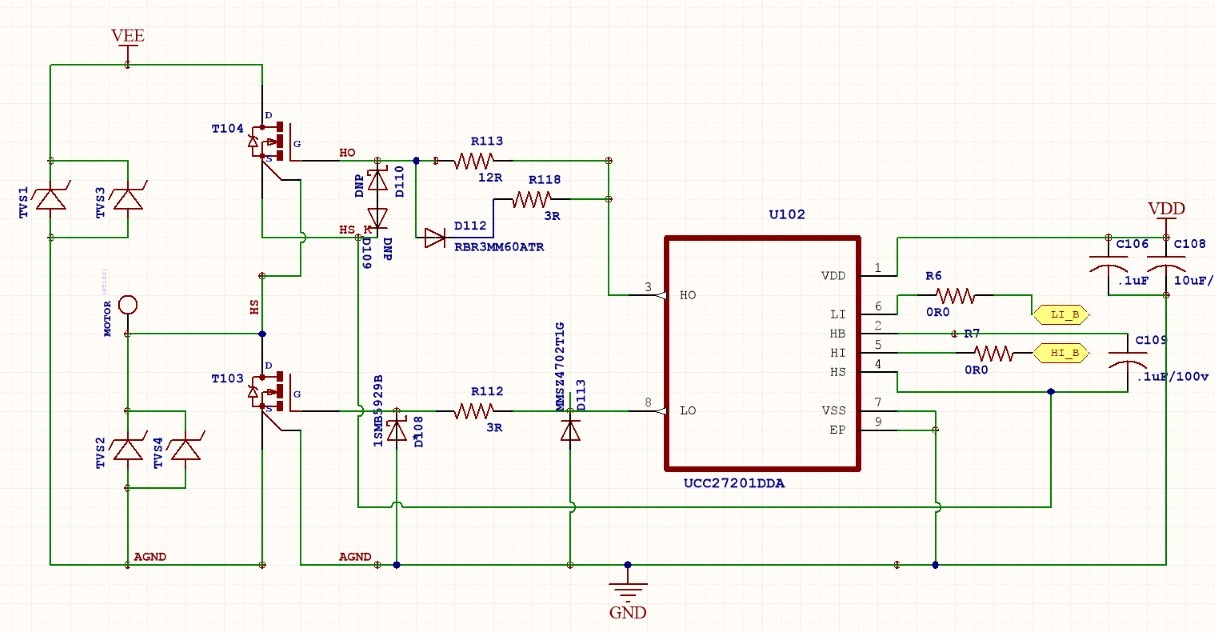

FET:大型 SOT-227 VS-FA72SA50LC,带255nC/10nF门。

VDD:12伏

功率:48V

栅极(高)=12欧姆,(二极管+3欧姆用于下拉)

栅格(lo)= 3欧姆

Lo由16V Zener保护

HS受75V TVS保护

升压电容器多种多样:从.1uF到2.2uF (大部分为.1uF)。 未找到与故障的关联

在驱动器+CPU的12V+5V启动之前,FET始终接通48V。

该问题很难在工作台上重现和捕获,但在原型测试期间经常出现。 开机时,故障始终在第一秒钟左右发生。 电源似乎良好,尽管Hin/LIN可能在VDD达到12伏之前驱动(5伏)。

照片应显示在我的名字后面。

谢谢!

Rick