Other Parts Discussed in Thread: TPS543C20, TPS543C20A, TPS543B20

主题中讨论的其他部件:, TPS543B20

您好,

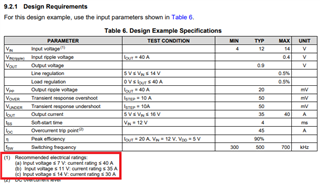

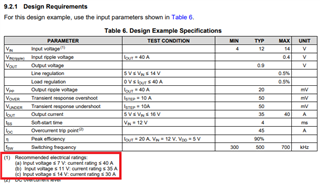

我的客户 在 TPS543C20数据表中找到了电流额定值建议,如下所示。

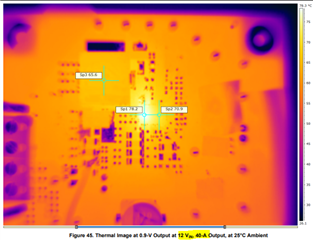

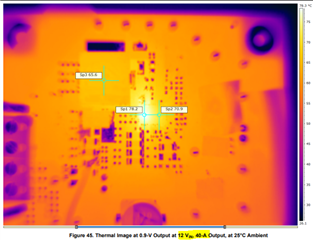

数据表中也包含12伏输入电压下40A的测试结果,如下所示:

为什么有建议的电流额定值?

TPS543C20用户是否必须遵循这些建议?

如果未遵守根据输入电压确定的建议电流额定值,可能会出现什么问题?

谢谢你。

JH

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: TPS543C20, TPS543C20A, TPS543B20

您好,

我的客户 在 TPS543C20数据表中找到了电流额定值建议,如下所示。

数据表中也包含12伏输入电压下40A的测试结果,如下所示:

为什么有建议的电流额定值?

TPS543C20用户是否必须遵循这些建议?

如果未遵守根据输入电压确定的建议电流额定值,可能会出现什么问题?

谢谢你。

JH

您好,Miller:

感谢您的回复。

客户从TI工作台下载了以下模拟文件,作为TPS543C20A。

(TI工作台不支持TPS543C20)

e2e.ti.com/.../WBDesign80_5F00_Load-Transient_2D00_7.pdf

在相同条件下使用TPS543C20是否存在任何问题?

谢谢你。

JH

要从13V输入安全地在35A的电流下操作TPS543C20,您需要对电源输入旁路及其返回散热垫接地进行仔细的布局。 我还建议包括一个SW至PVIN缓冲器(而不是典型的SW至PGND缓冲器) SW至PVIN缓冲器将在低压侧FET关闭期间减少PVIN至SW的应力,比SW至GND缓冲器减少更多。

我还建议将两个4.7nF或6.8nF 0402电容器放在PCB背面的PVIN引脚下,在散热垫的PVIN和PGND之间。在 设计规则允许的情况下,将通电管放置在靠近PVIN引脚的位置。 此电容器具有大约100MHz的自谐振频率,有助于抑制PVIN上的开关转换应力,并在高侧FET关闭期间降低PVIN至SW的应力。

您好,Peter,

感谢你的帮助。

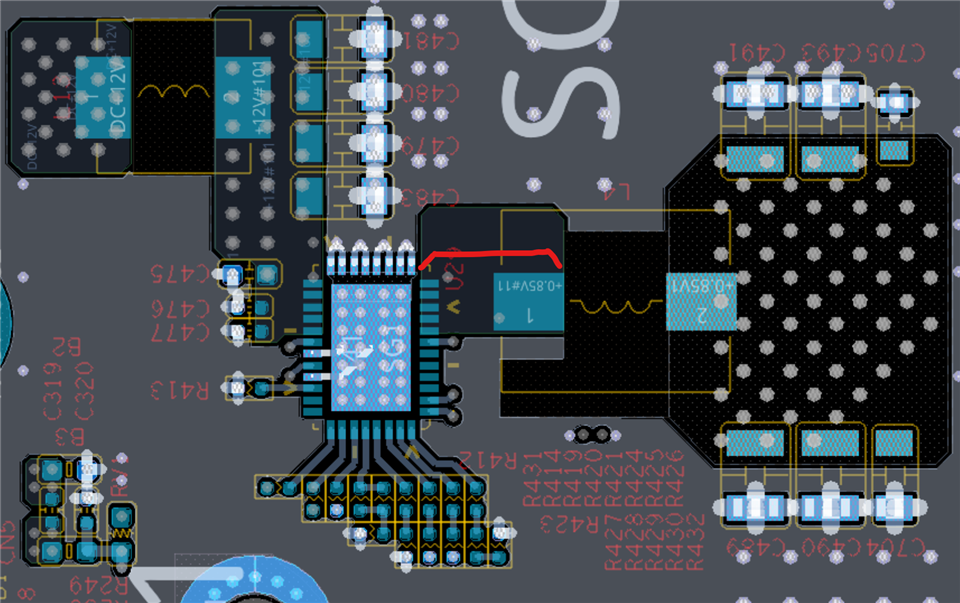

请查看TPS543C20的原理图和插图,以确保其设计正确,成为您的指南吗?

e2e.ti.com/.../TPS543C20RVFR_5F00_Review.pdf

谢谢你。

JH

请参阅 TPS543B20 TPS543C20A TPS543C20 Excel计算器工具和核对表(位于TPS543C20产品文件夹中的设计与开发和设计工具与模拟- https://www.ti.com/product/TPS543C20#design-tools-simulation下)

它包括一个设计工具以及原理图和布局清单。 如果您在查看原理图或设计后有特定的问题或疑虑,我们可以查看这些问题或疑虑。

对于12V @ 500kHz和1nF电容器,缓冲器电阻器的功耗约为72mV,这高于1005 (0402)电阻器的1/16W额定值,因此我肯定会建议选择至少1608 (0603) 1/10W电阻器封装。

我会建议C475,C476和C477的附加接地通孔,以使其最有效。 虽然它们的衬垫内的VIA电容器良好,但每个电容器只有1个VIA电容器具有一定的限制性。

如果有空间将6.8nF电容器放在主板的背面,并通过VIN,和阵列直接连接到散热垫的背面,则更适合减少开关节点振铃。

关于远程感应线: 我是否正确读取幻灯片,它们大约为150 mm (6英寸)? 这看起来相当长,由于分布电感和远程旁路电容,可能会引入一个功率路径极, 因此,我建议在R415和R417之间添加一个电容器,从接近L4的输出电压回至网络,用于在高频率下抵消增加的极并提高回路稳定性,

为GND和PVIN缓冲器提供2个导通孔,将SW节点带到PCB背面,为它们连接到VIN和GND提供2个导通孔 ,也有助于降低其环路电感。

我还建议将SW区域从TPS543C20缩小到L4。

另外,我认为一切都很好。