大家好、

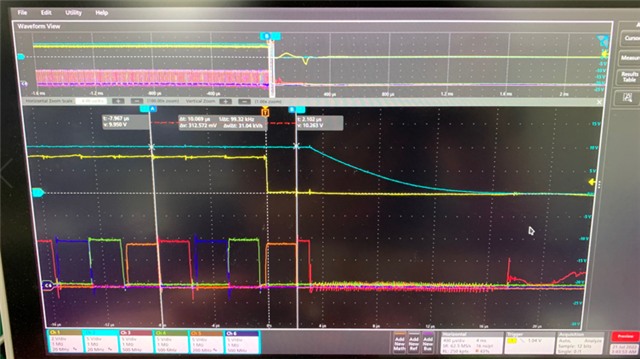

这个问题发生在输出短路测试期间、我的客户将 LM5170配置 为降压模式、Fsw 大约为100kHz。

在发生输出短路事件后、SS&EN 引脚被外部信号拉低、 但我的客户仍然可以观察到高侧 VGS 被随机错误触发、这会损坏外部 MOSFET。 Vgs 错误触发的时刻与下一个开关周期的上升沿保持一致。

您能否帮助评论此问题背后的可能原因?

CH1:IC SS 引脚、CH3:Mos Vds、CH4:Mos Vgs

CH1:IC SS 引脚、 CH3:Mos Vds、 CH4:Mos Vgs

谢谢、

查尔斯