Other Parts Discussed in Thread: TPS1663

您好!

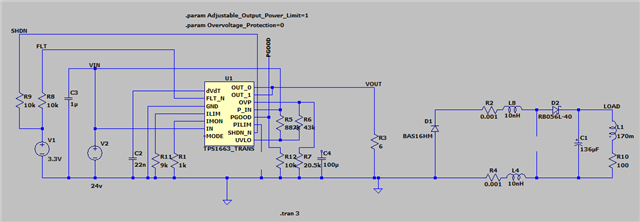

我尝试在 LTSpice 中模拟 TPS1663的基本运行特性、我在仿真过程中观察到一些意外行为。

以下是测试场景…

测试案例1:

电流限制为2A

负载电流为1A (电阻负载)。

观察结果:输出负载小于过流限制设置(2A)、因此输出电压与输入相同、并且不存在预期行为的故障。 但 PGOOD 信号保持低电平、而正常运行时应为高电平有效。

测试案例2:

电流限制设置为2A。

负载电流为4A (电阻负载)

观察结果:输出负载大于过流限制设置(2A)、在0.2Sec 时输出电流从跳闸限制(2A)变为零、但它在0.9秒时恢复到跳闸限制、并且是连续的。 当跳闸发生时、输出电压会上升到12V 并变为零、然后再次恢复到12V。 MODE 引脚设置为锁存操作、但观察到输出已恢复。 此外、无论跳闸与否、故障始终置为有效。

您能否主要了解一下 PGOOD 和 FAULT 引脚的意外行为。

连接了用于仿真的 SPICE 模型。

此致

Hari K