主题中讨论的其他器件:LM51561、 LM3488

我想在 LM51561上使用外部时钟同步功能。

计划在3.3V 电平、120kHz 的 FPGA 中使用外部时钟。

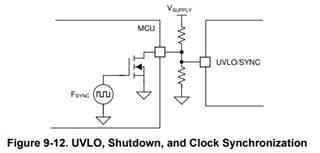

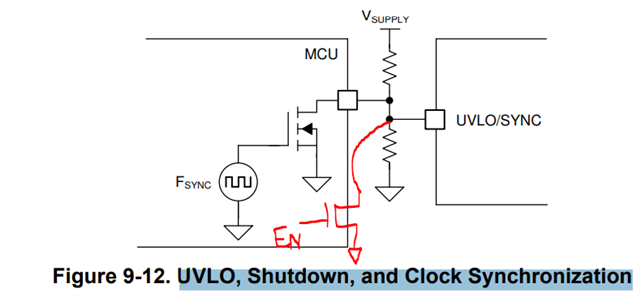

有关详细信息、请参阅下面的图1。

数据表中未找到所需外部时钟的规格。

数据表第6页上有与 UVLO/SYNC 相关的电气属性、但我不太理解。

工作方案如下。

当系统首次启动时、它以 RT 设置电阻值运行、并且当 FPGA 下载并初始化时、FPGA 将提供外部时钟。

我在下面向您提出三个问题。

1.询问同步信号阈值规格(高电平、低电平)。

2.在下面的图1中、我询问是否有任何问题、即使您像使用 R13和 C19一样使用它也是如此。

3.如果您可以像下面图1中的 R13和 C19那样使用它,请查询设置 R/C 值的公式。

4. 如果有更好的方法,请提出建议。

作为参考、下面的示例是 LM3488数据表中的一个外部时钟规格示例。