主题中讨论的其他器件: UCC28951

大家好、

它是一个使用 UCC28950的应用、被设计成一个从器件并从外部以190kHz 的同步频率运行。

通常、在一种模式下、C 和 D 驱动输出的高/低电平时间会变长。

当我过去检查过线程时、我确认当占空比为90%或更多时、会出现相同的模式、并且会出现过流状态。

作为解决方案、我尝试更改为 UCC28951、但该模式仍在发生。

请就该模式的原因和解决方案向我们提供一些建议。

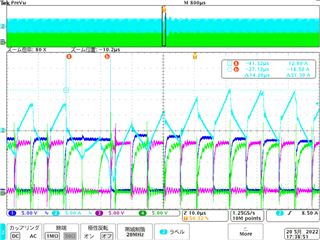

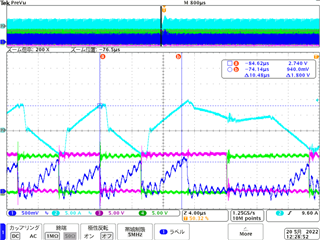

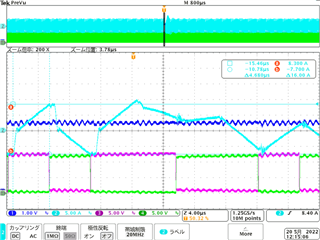

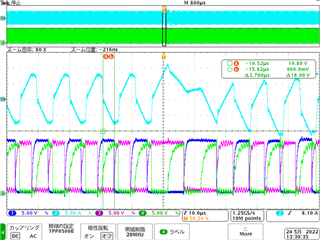

请参阅下面的波形;

-CH1 C_FET_Vgs

CH2变压器电流

-CH3 D_FET_Vgs

-Ch4 B_FET_Vgs

模块1.

模块2.