请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:BQ77915 大家好、

您能帮我们客户解决问题。

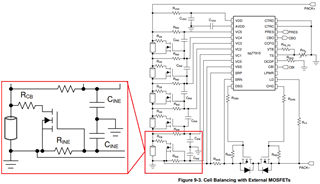

我对 BQ77915 BMS 芯片有疑问、文档中显示的设计电路。

在什么情况下、图片中突出显示的晶体管会打开。 看起来栅极和源极连接到0V。

另请注意、根据我的理解、VC0至 VC5似乎是输入、不会导致这些平衡晶体管打开和关闭、但我可能会错

此致、

Jonathan

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好、Jonathan、

连接到电芯1的 FET 导通所需的栅极偏置电压由 连接到 VC0的电阻器 Rine 生成。 确保 Rine 为1kOhm、Cine 为0.1uF。 栅极的阈值电压应小于1.7V。 数据表第9.3.4节中的图9-2概述了这一点。 VC0确实有助于平衡晶体管的导通和关断。 堆叠器件时、VC5不会用于打开 VC6的晶体管。 上部器件的 VC0将会执行该操作。 确保下部器件的 VC5和上部器件的 VC0保持分离。

谢谢、

Caleb