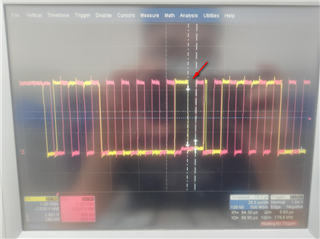

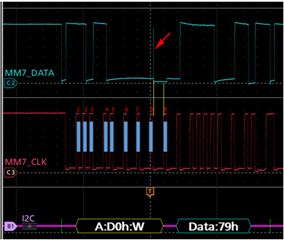

我想在 ACK 阶段对 SDA 和 SCL 进行时间差。 我该怎么做才能使 SDA 在 I2C 时钟拉伸阶段的早期变为低电平、如下所示?

或 SDA 拉至低电平的时间更长。 我该怎么做才能实现我的目标?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

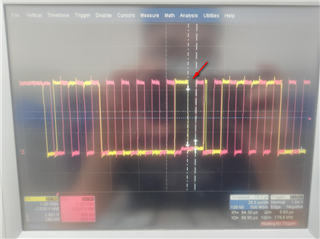

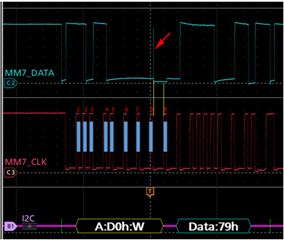

我想在 ACK 阶段对 SDA 和 SCL 进行时间差。 我该怎么做才能使 SDA 在 I2C 时钟拉伸阶段的早期变为低电平、如下所示?

或 SDA 拉至低电平的时间更长。 我该怎么做才能实现我的目标?