主题中讨论的其他器件: TPS65086

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Teik、

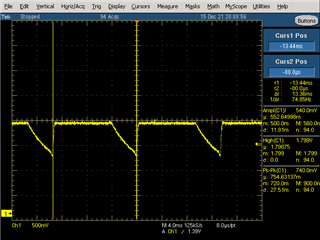

感谢您的提问。 从示波器屏幕截图中可以看到电源故障。 为了进一步研究、请提供 Buck1、Buck2、LS1和 Buck6启动的示波器截图。 这可能能够识别何时发生电源故障。

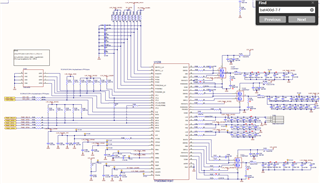

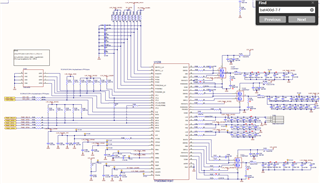

另请 参阅 TI.com 上 TPS650864产品文件夹(TPS65086x 原理图和布局检查清单(修订版 A))中提供的原理图检查清单、并以 PDF 格式提供原理图。

谢谢、

路易丝

您好!

您所指的 LS1是什么?

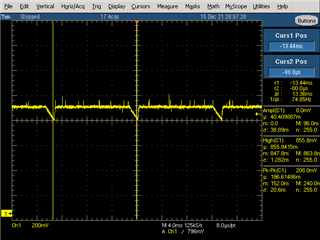

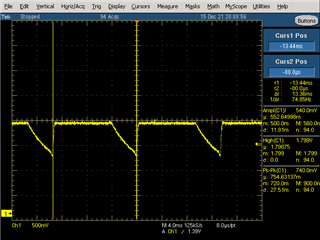

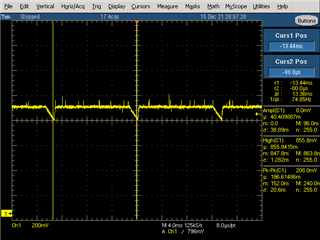

我已经捕获了上电期间12V 输入源、BUCK2、BUCK1、BUCK6的波形:

我们还测量了 CTL1、它在3.3V 时始终保持稳定、通过100k 电阻上拉至 LDO3P3 (引脚54)。

顺便说一下、我们有上拉 CTL3 (通过100k 电阻器上拉至 BUCK1 1.8V 输出)和 CTL2至 GND (针对0.6V 的 VTT LDO 输出)。

您好、Louise、

我有一些调查结果需要更新。

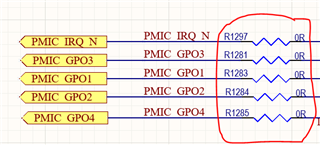

如果我移除连接到 FPGA 的所有 GPO 跳线:

对于该配置中的 CTL:

CTL4 =通过100k 上拉至 BUCK1 1.8V、也被连接至 GPO3

CTL5 =至 GND

CTL3 =通过100k 上拉至 BUCK1 1.8V

CTL2 =至 GND

CTL1 =通过100k 上拉至 LDO3P3 (引脚54)

CTL6 =通过100k 上拉至 BUCK1 1.8V 并连接至 GPO1

在这些配置下、输出现在看起来稳定而没有骤降。

我们观察到、CTL5上拉至1.8V 时、会发生骤降。 有什么可能的原因?

您好、Louise、

遗漏了信息。

我们还将 PVIN3/4/5 (引脚11/24/21)连接到 V5ANA (引脚57)。

如果没有这种连接、我们观察到骤降、并且 CTL4 (在本例中为 GPO3)不会置为高电平。

但是、从数据表中可以看出:"转换器(BUCK3、BUCK4和 BUCK5)用于调节的偏置。 电源必须与 PVINx 相同。 还有一个

内部负载开关、如果使用5V 电压、则将此引脚连接到 LDO5P0引脚。 使用可选的陶瓷电容器旁路该引脚、以提高瞬态性能。"

但是、我们不确定这首先与 BUCK1、BUCK2、BUCK6突降有何关系、也会影响 GPO3输出。

您好、Teik、

感谢您的更新和其他信息。

我仍在研究这一点、并将在下周初提供更新。

在此之前、您可以查看之前的 E2E 常见问题解答主题并使用建议的调试建议: https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/992402/faq-tps650864-regulator-is-shutting-down-or-measuring-x-lower-than-expected---what-is-the-cause

最棒的

路易丝

您好、Teik、

感谢您的耐心! 我已经查看了您在之前消息中提供的信息、下面是我的反馈、它将特定应用于 TPS65086401 OTP 配置。

谢谢、

Brenda