请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS274160 各位专家:

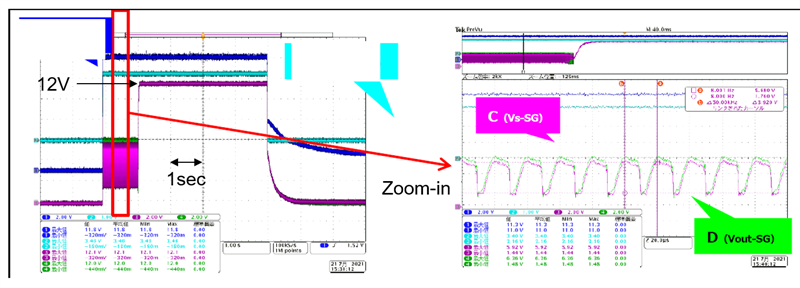

由于客户的外部组件、Vs 引脚和 Vout 引脚上施加约50kHz 的3.5Vp-p 纹波持续1秒。 EN 引脚通过3.3V 拉高。 经过1秒后、向 Vs 引脚提供12V 电压。 此时、启用 EN 引脚的输出电压为12V。 我们不认为这违反了 HS 开关的绝对最大值。 下面是波形。

在 VS 引脚和 Vout 引脚上施加电压纹波是否存在任何问题?

此致、

Uchikoshi