主题中讨论的其他器件:TPS746EVM-009、 TPS746

您好!

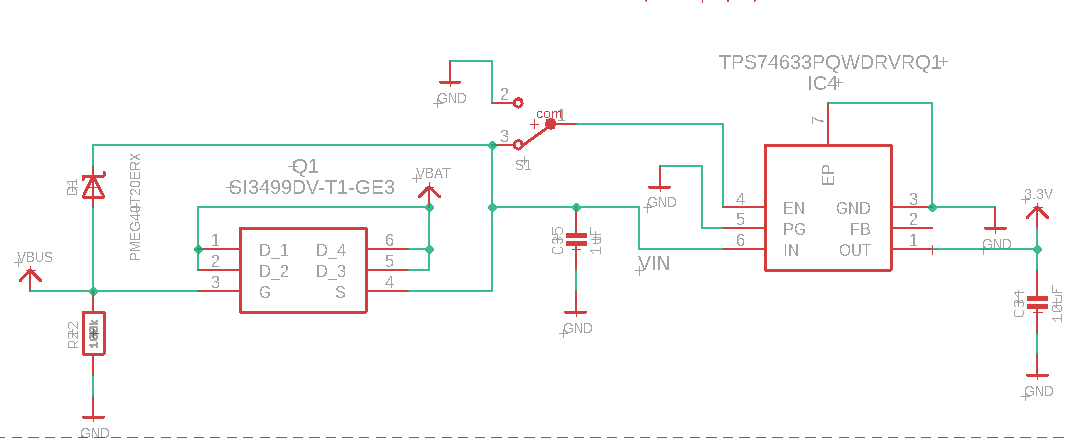

我 在设计中使用 TPS74633PQWDRVRQ1 来提供便携式设备、如下所示。 当输入电压来自锂聚合物电池 (输入电压~ 3.4-4.2V)时、输出电压为~3.3V。 但是、当我从 VBUS (输入电压~ 4.5-5V)供电时、输出固定为3.45v。 我想知道 这里发生了什么。

另一个问题是我使用开关来传输 EN 信号。 如果输入电压来自电池、则当 EN 连接到 GND 时、开关工作正常、芯片的输出为0v。 当输入电压来自 VBUS 时、即使 EN 信号 连接到 GND、芯片也会产生输出、无论 EN 信号如何、输出都是3.45v。

谢谢。