请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS7A26 客户对 TPS7A26电源/复位电路性能有问题。

数据表显示、当 Vout 超过目标 Vout 电压的93%时、PG 悬空至上拉电压、而当 Vout 降至目标 Vout 电压的90%以下时、PG 使用漏极开路拉低。 是这样吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Carl、

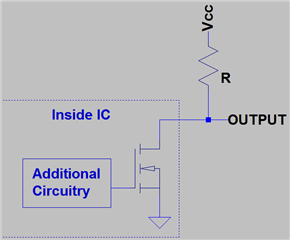

请参见下面的图像(从 DigiKey 获取)。 当输出高于目标值的93%时、PG 引脚被驱动为高阻抗(即 FET 被关闭)。 在这种情况下、流过的电流非常小(仅漏源泄漏电流)、因此 R 两端的压降非常小、PG 引脚会看到 VCC 电压。 当输出降至其目标值的90%以下时、FET 导通、电流流动、从 R 上的 VCC 下降大部分电压、从而使 PG 引脚电压接近0V (通常为~0.4V 或更低)。

您能否分享更多有关客户应用的详细信息?

此致、

Nick