大家好、

输出电容值对 PSRR 性能有多大影响?

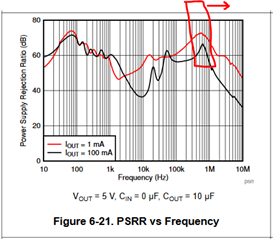

我想申请 TPS7B8133-Q1和 TPS7A6633-Q1的 PSRR 与频率间的关系图、就像 TPS7B8133-Q1数据表中的图6-22一样。

我的条件是 Cin = 1.0uF、Cout = 2.2uF、Vout = 3.3V、Iout = 10mA

图6-22为 Cin = 0uF、Cout = 10uF、Iout = 1mA 或100mA

我想知道 CIN/Cout 值对 PSRR 性能有多大影响。

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

输出电容值对 PSRR 性能有多大影响?

我想申请 TPS7B8133-Q1和 TPS7A6633-Q1的 PSRR 与频率间的关系图、就像 TPS7B8133-Q1数据表中的图6-22一样。

我的条件是 Cin = 1.0uF、Cout = 2.2uF、Vout = 3.3V、Iout = 10mA

图6-22为 Cin = 0uF、Cout = 10uF、Iout = 1mA 或100mA

我想知道 CIN/Cout 值对 PSRR 性能有多大影响。

此致、

您好、Shinji、

输出电容器主要在高频时影响 PSRR、超出 LDO 的带宽。 TPS7B81-Q1的图形是使用10uF 输出电容捕获的。 当输出为2.2uF 时、1MHz 左右的高 PSRR 峰值将转换为稍高的频率、然后滚降。

这些图中未捕获输入电容器的影响。 PSRR 通常在没有 Cin 的情况下获取、因为添加输入电容器会使测试设备更难将高频纹波驱动到 LDO 中。 如果您增大 Cin、通常可以预期输入纹波的振幅会减小、但您必须评估系统以确定其增大的幅度、因为这也取决于驱动 Cin (和 LDO)的源阻抗。

谢谢、

斯蒂芬