请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LM5119 您好、TI 专家。

客户询问了 LM5119的 UVLO 运行情况。

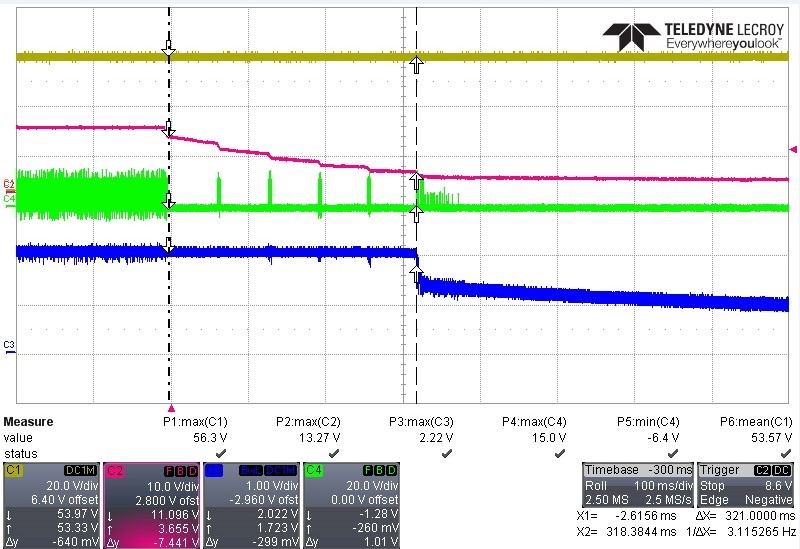

-条件:当强制 UVLO 关闭时,在外部电路延迟321ms 后 UVLO 关闭。

-问题)

在 UVLO 电平不从1.2V 下降到0.4V 的条件下、低侧 FET 间歇性工作。

(单通道:输入、双通道:输出、三通道:IC UVLO、四通道:低侧栅极)

在上述条件下、UVLO 引脚电压被施加、并且处于负载 S/W 关闭的开环状态。

如果低侧栅极波形保持不变或根本不出现、但波形看起来像是保护操作、这是很有意义的。

我想知道原因。 是否有特定的保护电路?

此外、还有一个应用了 LM5119的原理图。

但是、由于客户不希望披露原理图、请提供您的电子邮件地址。 我将向您发送原理图。

请检查并回答。

谢谢你。