你(们)好

我有一个由 LM5106驱动的半桥。

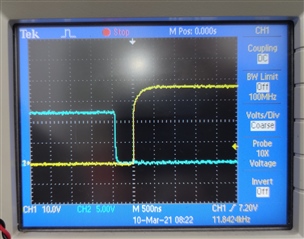

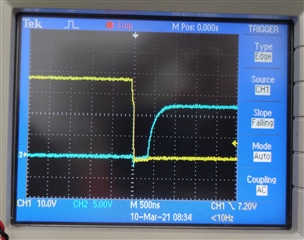

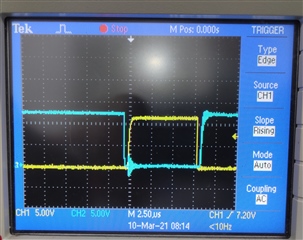

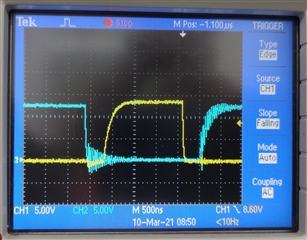

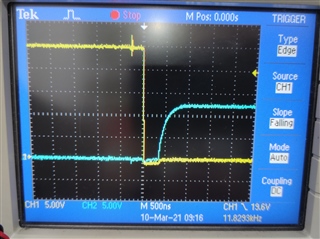

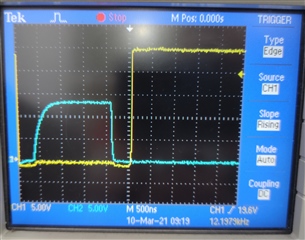

高侧和低侧 Vgs 之间有大约400nS 的死区时间。 但这种高侧和低侧 MOSFET 在 VDS 下的死区时间没有影响。

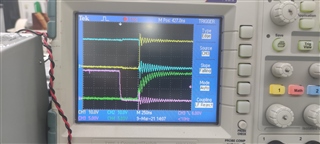

如图所示、CH3 (绿色)和 CH4 (紫色)是 Vgs 高侧和 Vgs 低侧。

*噪音是由于连接到示波器的接线造成的*

CH1 (黄色)是高侧 MOSFET 的漏极源极电压、而 CH2 (蓝色)是低侧 MOSFET 的漏极源极电压。

即使我拔下电机插头、信号也是完全相同的。

无死区时间的开关在几个 ns 内发生、但仍会对直流线路和电机电流产生影响。

我已经使用 RDT 并增加了死区时间、但它仍然是相同的 VDS 高侧和低侧一起变化。

该原理图与数据表中推荐的 LM5106原理图相同

我需要知道这一问题的原因是什么。