您好!

在 Jacinto7 EVM 设计中、TLV7103318的1.8V 和3.3V 输出与0欧姆电阻器短接、如下图所示。 这里描述了如果我们想要实现3.3V 输出、EN1和 EN2都应设置为高电压电平。 但我想、1.8V LDO 将灌入电流、而3.3V LDO 将拉取电流。 这两个 LDO 内将有一个圆形电流。

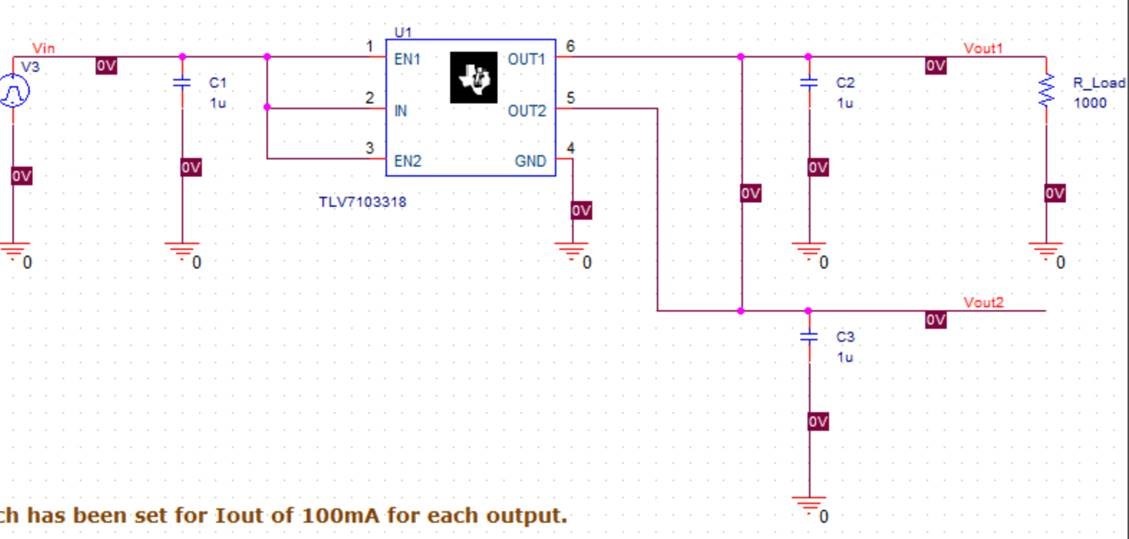

由于我不知道1.8V LDO 是否会灌入电流、因此我使用 PSpice 模型完成了一个简单的仿真、如下图所示。

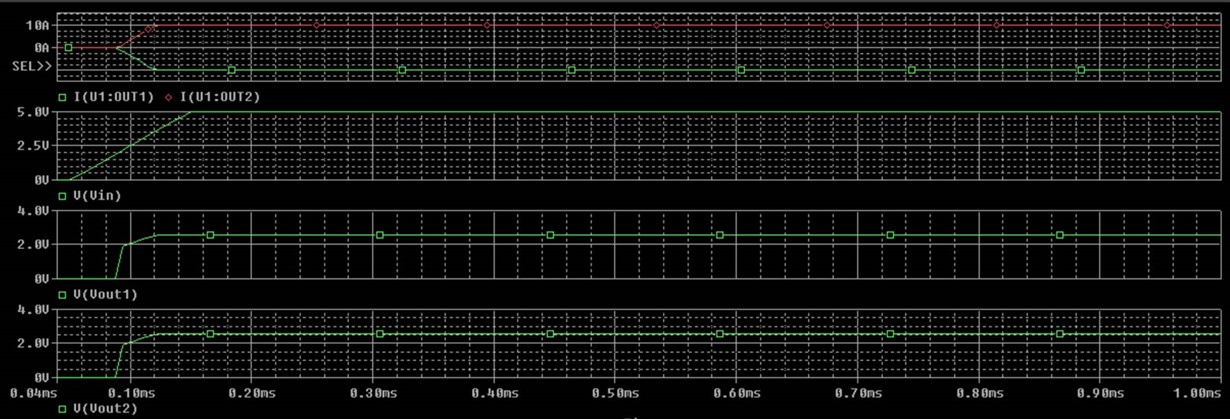

仿真结果与下面的波形相同。 可以看出、这两个 LDO 内部大约有10A 的圆形电流。 该结果也使我感到困惑、因为数据表上的电流限制规格仅为几百 mA。

您能对此进行一些解释吗? 该问题是导致我在仿真中出错还是无法这样使用? 由于我的客户对 EVM 设计的这一部分感到困惑、请帮助提供有关 TLV7103318这种用法的一些说明。 为什么可以这样使用它、或者为什么不能使用它...

谢谢、

Andrew