您好!

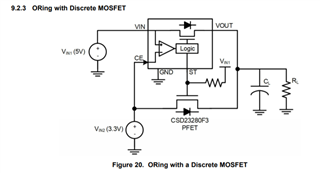

我正在尝试使用 LM66100 + PFET 实现此逻辑:

- 5V 存在:Vout = 1V8

- 5V 缺失:Vout = 3V

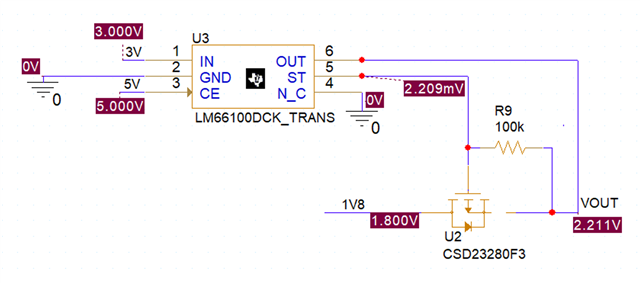

这是我的原理图:

一方面、这似乎不是一种有效的拓扑、因为:(1) 仿真电压(如原理图所示)表明 LM66100在输入电压大于输入电压的情况下驱动输出电压、(2) 我猜测 当输入电压大于输出电压时、LM66100内部 FET 的体二极管将导通。

另一方面、LM66100仿真模型显然是错误的(根据 这 一点和 这一点)、因此我可能会碰到一个错误。

这是 LM66100的有效拓扑吗?

谢谢、

David