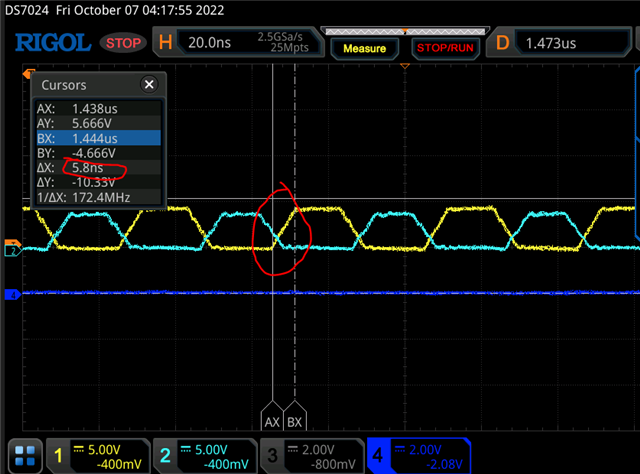

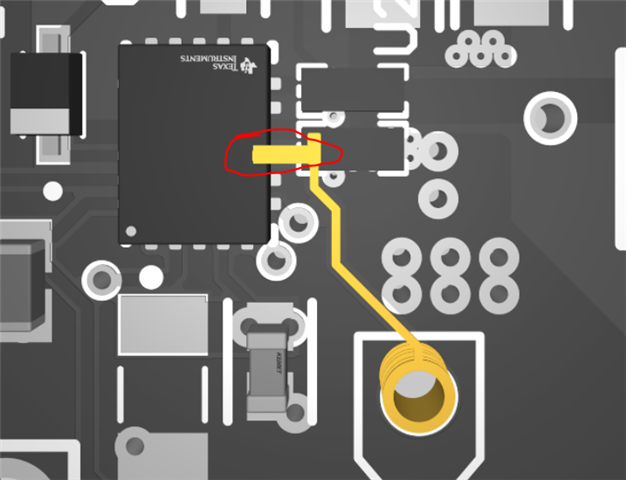

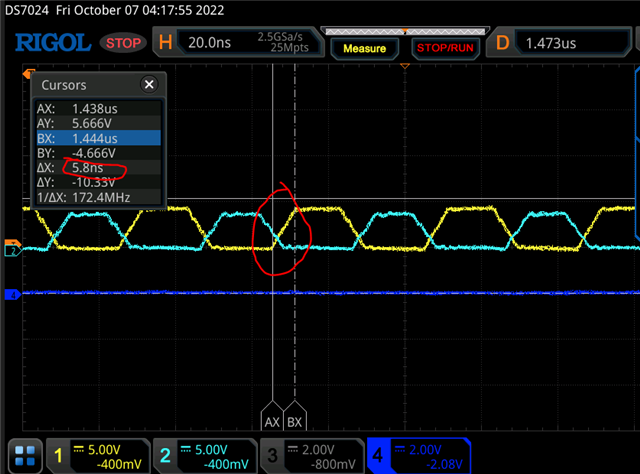

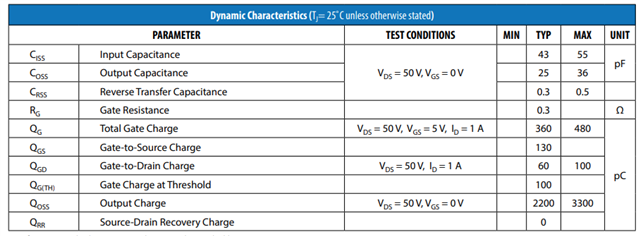

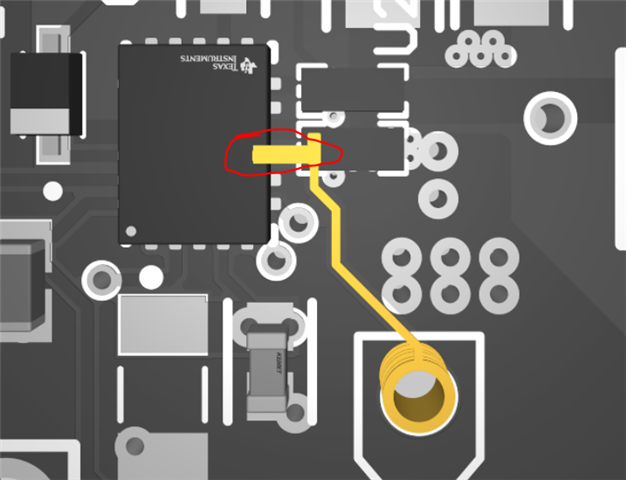

在我们的设计中、它是 Hbridge GaN EPC8010 (Ciss=43pF)栅极驱动器 LMG1210。 从 gatedriver 到 EPC8010的布线超短、如所附图片所示、两者之间没有栅极电阻器。 有用于探测的孔/过孔的走线(与 LMG1210EVM 中的封装相同)。 因此、上升/下降时间应在 ns 内、而我们测量 的是6ns、如示波器迹线所示。 您能帮助我诊断发生了什么情况吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

在我们的设计中、它是 Hbridge GaN EPC8010 (Ciss=43pF)栅极驱动器 LMG1210。 从 gatedriver 到 EPC8010的布线超短、如所附图片所示、两者之间没有栅极电阻器。 有用于探测的孔/过孔的走线(与 LMG1210EVM 中的封装相同)。 因此、上升/下降时间应在 ns 内、而我们测量 的是6ns、如示波器迹线所示。 您能帮助我诊断发生了什么情况吗?

您好、胜南、

是的、我可以帮助诊断。 您的信号路径看起来很好。

如果您的示波器上有选项、您能否将通道带宽设置为满?

您可能需要更高带宽的示波器来测量上升时间。 Rigol DS7024的带宽仅为200MHz。 根据经验、您可以使用公式带宽= 0.35/上升时间来计算所需的带宽。 使用此公式、我得到了负载上升时间的100MHz 带宽。 然后、您需要将带宽提高3到5倍以捕获信号的真实形状。

此外、对于示波器、所有通道之间是否共享2.5 GSA/s 采样率、或者每个通道是否具有2.5 GSA/s 采样率?

此致、

Edthan Galloway

盛南

您将需要对信号使用正常模式。 峰值模式也可以工作、但我的示波器没有此模式、因此我以前没有尝试过。

高分辨率模式以牺牲带宽为代价提高分辨率和噪声。 我认为这对您没有帮助。

平均模式对多个通道上的信号进行平均值计算。 这将降低电路中的噪声、但不会为我们提供更高的分辨率。

顺便说一下、DSO724将"通道带宽"称为"带宽限制"。 您可以对通道应用带宽限制以减少您看到的噪声量、但 带宽限制会使高频信号衰减。 您将需要禁用此功能、但看起来您已经禁用了它。

此致、

Edthan Galloway

非常感谢您的快速响应。 我能够如图所示正确测量。

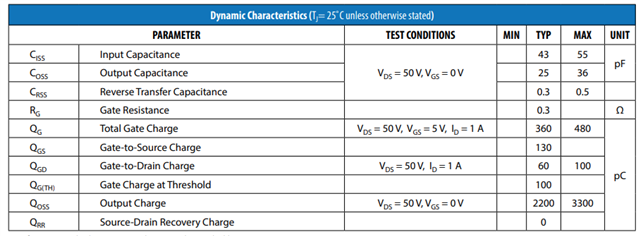

死区时间设置为2ns、开关频率为25MHz。 在打开和关闭时都有很大的振荡。 当在 Hbridge 上施加直流链路电压时、振荡会导致击穿。 当我检查降级板时、栅极驱动信号非常干净(第二个波形)。 根据演示板的原理图、栅极电阻为0。 将我的板与降级板进行比较、我板上的 GaN 具有小得多的栅极电容(43pf 与700pf)、栅极环路更小。 那么、我想知道演示板没有振荡的神奇之处是什么? 如何调节电路板?