主题中讨论的其他器件: 、CSD18540Q5B

我正在计算由 LM5170电流控制器驱动的功率级 MOSFET 的功率预算。 高侧电压的标称值为48V、低侧的电压范围约为5V 至18V。 我尝试布置 PCB 并选择合适的 MOSFET、以确保设计能够处理30A/相电流产生的热负载。 此设计与 LM5170-EVM 的设计有点相似、但我希望避免并联 MOSFET、从而创建一个紧凑的电源环路、从而更大限度地减少振铃。 更具体地说、我使用 TI 文档 SLPA005中建议的布局作为功率级的模板。 我相信我在热可行性的边缘、因此、我希望确保我正确理解 MOSFET 功率耗散的组件... 尤其是开关损耗。

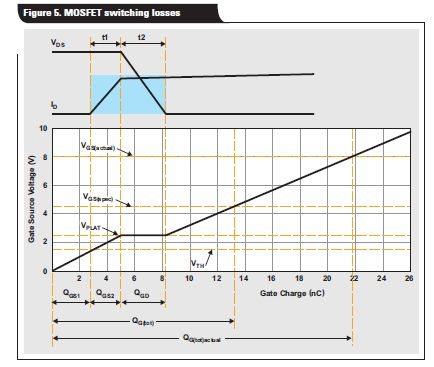

LM5170-Q1数据表(TI 文档 SNVSAQ6B)中的公式(55)和(56)提供了上升和下降时间近似值、可用于估算 MOSFET 本身的开关损耗(即不包括驱动器损耗)。 这些公式是否正确与栅极电阻(外部或 MOSFET 内部)无关、即栅极驱动器可被视为接近理想的电流源? 这些公式包括一个称为 Qg 的栅极电荷。 这是否与 MOSFET 数据表中列出的总栅极电荷 Qg 相同、或者这实际上只是完全导通 MOSFET 所需的栅极电荷部分? 使用 TI MOSFET 中的术语、例如、该栅极电荷是否为 Qg (th)+Qgs+Qgd? 以 TI CSD18540Q5B 的具体示例为例、公式(55)和(56)中使用的 Qg 是否为 Qg = 6.3nC + 8.8nC + 6.7nC = 21.8nC?