主题中讨论的其他器件:TPS544B25

您好!

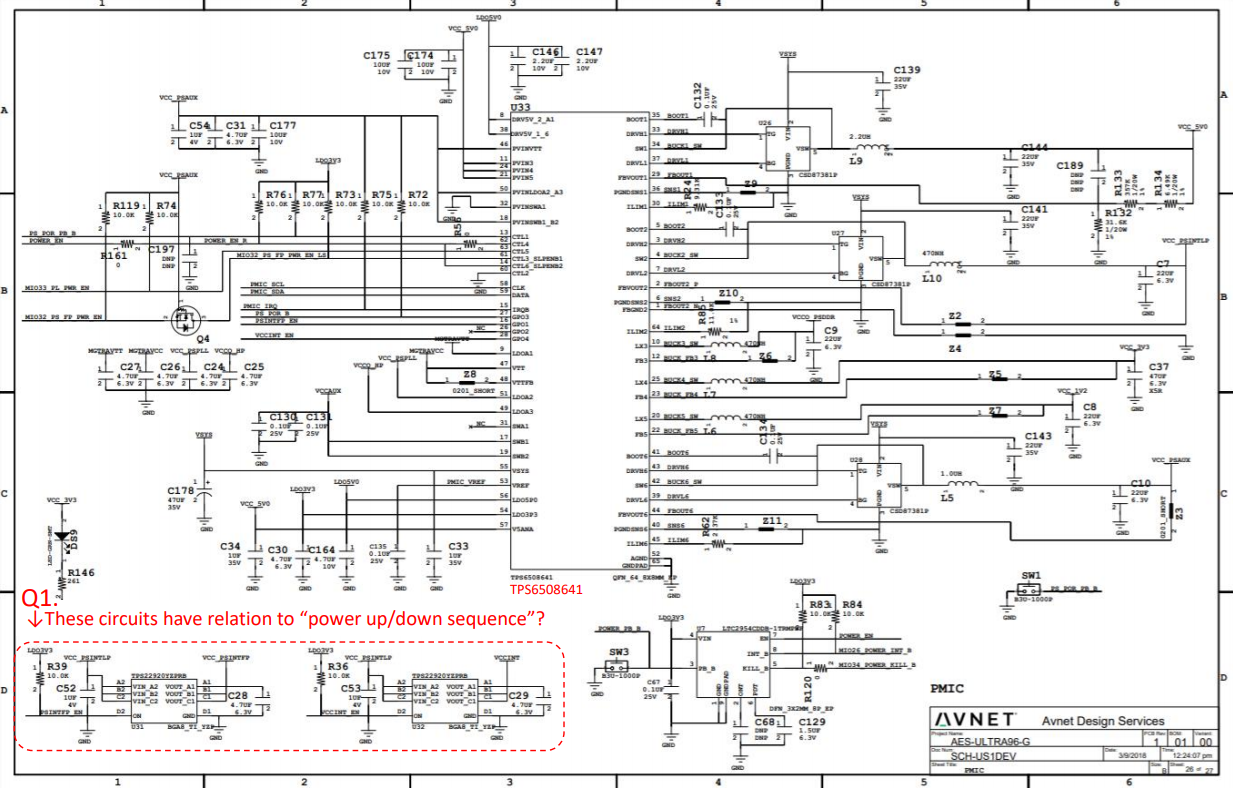

我正在开发安装了 Zynq UltraScale+ MPSoC (XCZU3EG-1SBVA484I)的原始 PCB。

我还采用了用于 Zynq UltraScale+的 PMU (TPS6508641)。 我选择的芯片是否正确?

请参阅 TPS6508641的数据表。

如图6-9所示,当连接时,我认为它们无法满足“VCC_PSPLL”和“VCCC_PSIO”之间的 Zynq UltraScale+上电序列。

请查看下图。

我已从 DS925 (Xilinx 数据表)中检查上电顺序。

我的理解是否正确?