主题中讨论的其他器件:TPS51220

您好、先生、

我们是否可以向您学习、

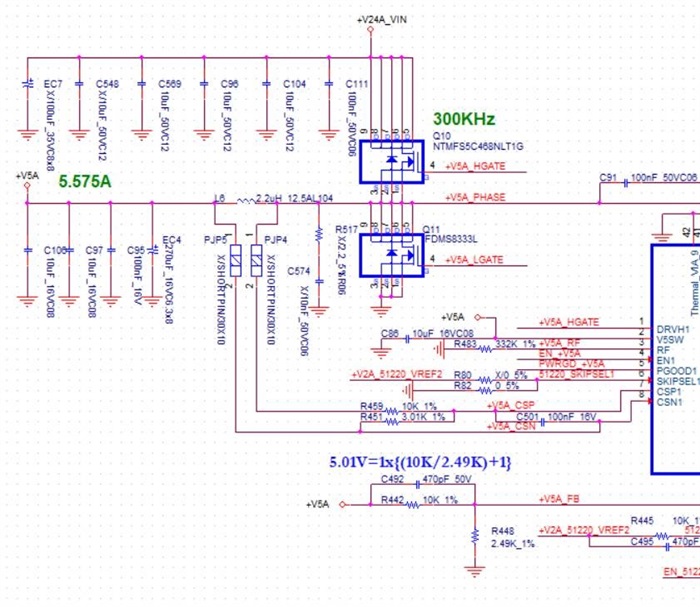

请参阅以下原理图和布局设计。

需要讨论一些设计概念

我们在 Phase1上针对+V5A 设计 TPS51220

关于 VIN 陶瓷旁路/高侧 Q10/低侧 Q11/输出旁路陶瓷和 EC4

问题1

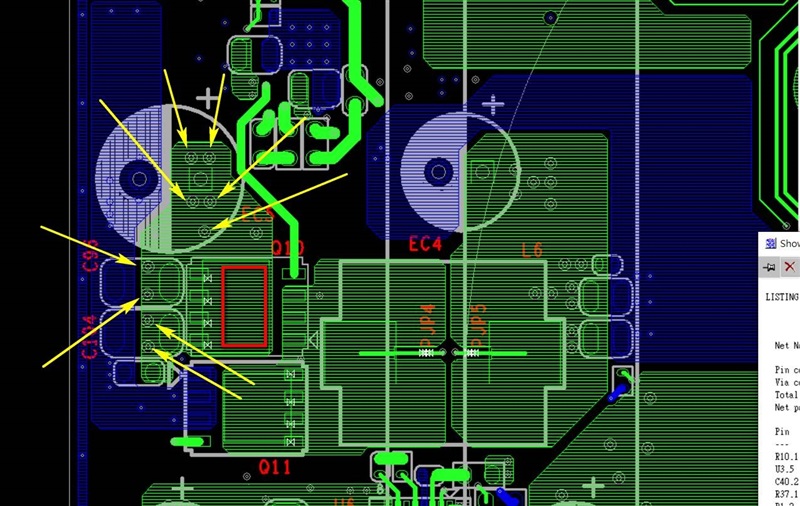

案例 I:VIN 由内部层通过过孔(黄色箭头)提供

案例 II:将这些通孔从当前位置(黄色箭头)更改为高侧 Q10排卸散热焊盘

可以提供更好的电源质量并降低 ESR/ESL

如果对于那些通孔有更好的位置、请建议! 谢谢

问题2:

输出旁路实心电容器的更多信息

我们是否应该为 EC4添加一些 GND 过孔、为电源返回路径添加输出陶瓷?

问题3:

PCB 顶部 EC4、我们是否应该在 EC4的顶部设计图案?