Other Parts Discussed in Thread: UCD7242, UCD74120, PTD08D210W

主题中讨论的其他器件: UCD74120、 PTD08D210W

大家好、团队、

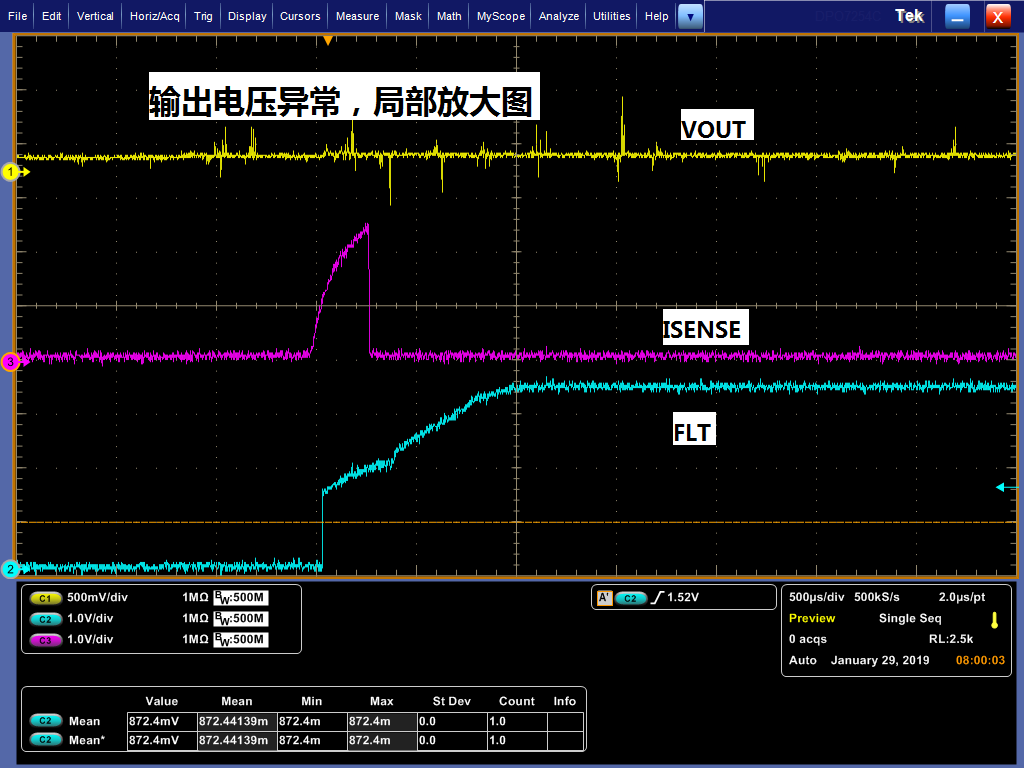

我的客户发现 PTD08D210模块中 UCD7242的 FLT 信号存在一些问题。 客户使用 Xilinx KC705的 SDK 中的参考设计来设计 SCH。 他们发现 PTD08D210中的一个将随机报告 FLT 故障、这主要发生在启动期间。

我让客户 增加启动时间、 这会带来一些好处、但仍然存在 FLT 问题。

下面是 FLT 问题的波形。

Sch 如下:

我们发现有一些 ucd74120应用、这提醒了与此类似的问题。 应该是 UCD7242的同一问题吗? 谢谢!