你(们)好

我们的客户正在评估 LP8860-Q1。 当下拉电阻器连接到 EN 引脚时、它们会发现 EN 引脚的一些泄漏电流。

(大约为130uA。)

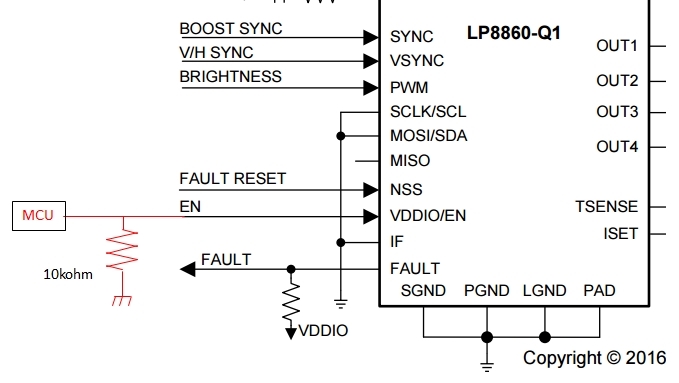

在其配置中、VDDIO/EN 引脚通过下拉电阻器接地、还连接到 MCU (连接到 GPIO 引脚以通过使能信号进行控制)。

在由启动的 MCU 进行控制之前、他们希望禁用 LP8860。 这就是它们将下拉电阻器(10kohm)连接到 EN 引脚的原因。

但是、EN 引脚的电压超过阈值电压的泄漏电流、LP8860在由 MCU 控制之前运行。

我们应该将下拉电阻器的值设置多少?

此致、

本志本