主题中讨论的其他器件: AM3352

您好!

我收到了客户的问题。

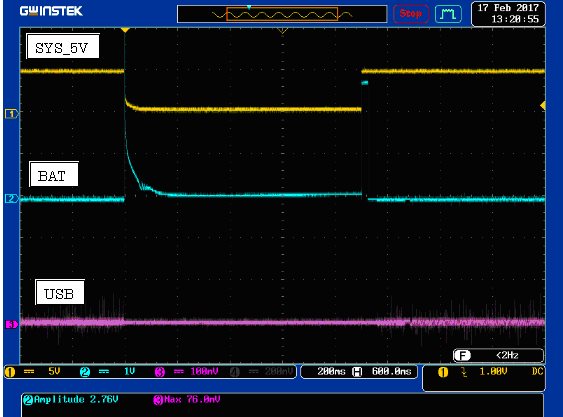

我们正在测试我们的一款产品、并获得错误的断电序列。

PMIC 未连接电池。 PMIC 寄存器设置为默认值、关断过程由 Linux shutdown -h now 命令启动。 硬件实现与 BeagleBone Black 原理图类似、但具有 FB_WLED LCD 背光实现。 我们的加电顺序正确:

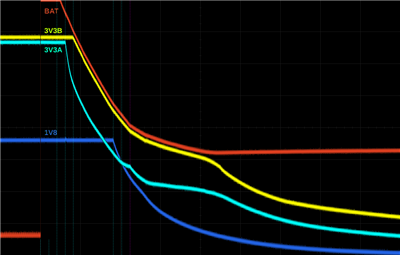

[SYS_5V]->[VDDS_RTC (LDO1)]->[LDO2 (3.3V)、LDO3 (1.8V)、LDO4 (3.3V)]->[VDDS_DDR (DCDC1)]->[VDD_MPU (DCDC2)、VDD_CORE (DCDC3)]。

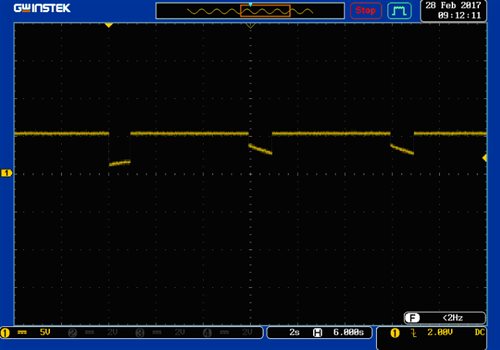

但我们的断电序列不是:

[SYS_5V]->[LDO2 (3.3V)、LDO4 (3.3V)]->[VDD_MPU (DCDC2)、VDD_CORE (DCDC3)]->[LDO3 (1.8V)]->[VDDS_DDR (DCDC1)]->[VDDS_RTC (LDO1)]。

这是什么原因?

这就是为什么 V_SYS 掉头...?

此致、

Kuramochi