Other Parts Discussed in Thread: CSD17312Q5, CSD17510Q5A, CSD18510Q5B, CSD18512Q5B

主题中讨论的其他器件: CSD17510Q5A、 CSD18510Q5B、 CSD18512Q5B

我创建了一个由 CSD17510Q5A (高侧)和 CSD17312Q5 (低侧)提供24V 输入电压的同步整流电路。

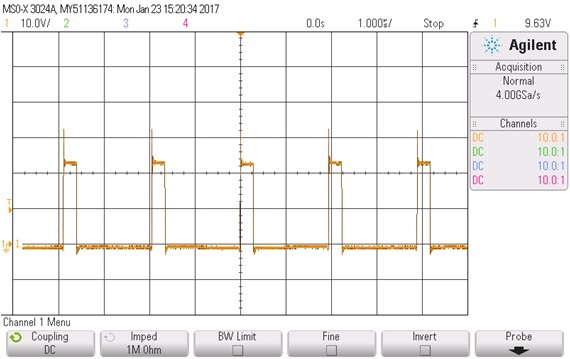

其开关频率为500kHz。

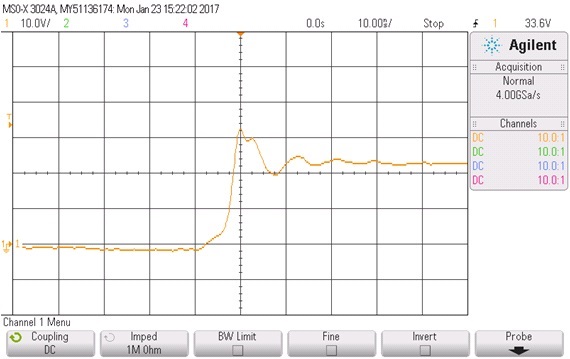

我的电路的开关节点处有可测量的振铃、其峰值电压约为35V。

超过30V 的峰值持续时间小于5ns、其峰值不是"平顶"。

我认为 CSD17312不处于雪崩模式。 对吗?

我的电路中的 MOSFET 是否存在任何问题?

此致