你好。

我对 UCC24630有疑问。

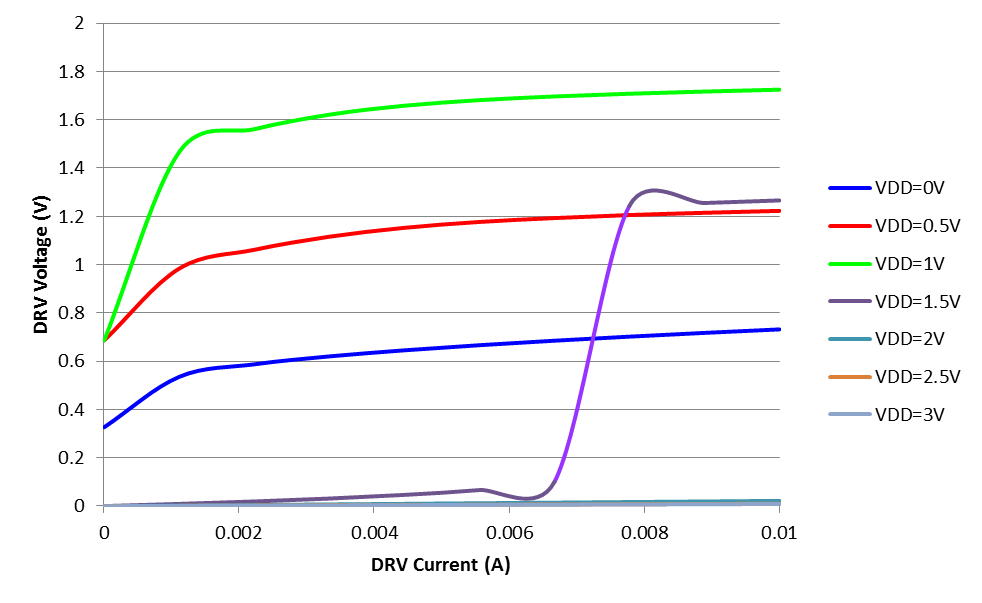

数据表 P5

启动时的 VDRVST DRV 下拉

我对下拉有疑问。

1应该在启动时工作。

它是否即使在停止时也能正常工作?(VDD =电压低于 UVLO)

2如果 VDD 的电压为2V 或更低、DRV 引脚的电压是否抑制为2V 或更低?

3如果 DRV 电压为2V 或更低、

考虑到在 DRV 端子和 VDD 端子之间的 IC 中内置了一个二极管。

二极管实际上是内置的吗?

如果内置了二极管、请告诉我该二极管的 VF 和 IF 的规格(最小值、最大值)

谢谢你