您好!

在执行 WCA 时、我注意到在整个温度范围内、VENILmax 在0.3V 时非常低。 我假设如果不在整个温度范围内使用、VENILmax 可能会增加。 我的应用结温仅为80C 或90C。 能否根据我的应用结温获得 VENILmax?

谢谢你。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

在执行 WCA 时、我注意到在整个温度范围内、VENILmax 在0.3V 时非常低。 我假设如果不在整个温度范围内使用、VENILmax 可能会增加。 我的应用结温仅为80C 或90C。 能否根据我的应用结温获得 VENILmax?

谢谢你。

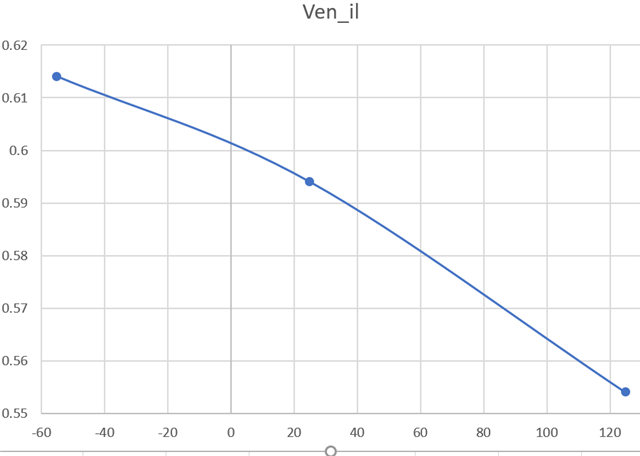

在仔细检查最近的特性批次后、在3V 电压下、30个器件的样本上的最小关闭阈值与此类似。

一种保守的方法是、根据上述趋势、只会因从125C 到90C 的变化而降低温度。 由于温度原因、这只能实现大约13mV 的电压。

也可以保守地降低由于 VDD 差异导致的偏移。 2.375至3V 阈值的变化是 ~80mV 的增加。

因此、保守的增加将允许13mV + 80mV = 93mV 的漂移。 因此、几乎为400mV。 该解决方案基本上仍会将我们的内部保护频带纳入数据表限制。

通常、该节点将由数字电压电平驱动、将节点接地通常不是问题。

我怀疑您在该节点上有上拉电阻、它们通过开漏输出被拉低。

此外、

我想指出的是、该器件没有内部软启动功能。 当在 VLDOIN 已激活后启用器件时、VLDOIN 电源在启动时可能具有挑战性。 IE、终端器的启动不依赖于源 VLDOIN 电源的软启动。

产品文件夹中显示了一种有效的解决方案来解决此问题。 在启动时、它依赖于使用晶体管来控制 VTTSNS 电压、从而控制浪涌电流。

此外、还有另一个新解决方案已经过验证、但目前尚未发布。 它非常简单、并且具有其他优势。

如果您的解决方案能够从中受益、我可以提供更多详细信息。 它涉及使用 VDDQSNS 的 UVLO 阈值、通过使用来自 VDDQ 电源的大小合适的隔离电阻器来启用/禁用器件。

这还将改善您的低电平启用阈值问题、因为 VDDQSNS 最大值的 UVLO 阈值约为750mV (典型值为0.78)。 目前未指定0.75、但将在将来添加到测试解决方案和数据表中、以满足此解决方案的要求。

如果您可以从此解决方案中受益、我可以通过电子邮件提供详细信息。

此致、

涉水

Kimberlee、

我将通过电子邮件向您发送有关备用软启动方法的信息。

此外、关于 FPGA 的电压。 这可能是通过特定的 IOL 指定的。

终端器的 EN 引脚为高阻抗、泄漏电流为+/- 1uA (25c)。 因此、它不会加载 FPGA 输出。 数据表仅显示25c、但整个温度范围内的泄漏电流也小于+/- 1uA。 低 nA。

如果节点上还有其他负载使其更接近输出的 IOL、那么我同意您的分析需要适应400mV。

如果您只有低于 IOL 的轻负载、则您将有更好的裕度来满足300mV Venil。

FPGA 数据表中可能有一个电压与 IOL 典型关系图、该图有助于了解额外裕度。

但是、如果您的系统将在 VLDOIN 已激活的情况下启用终端器、那么我建议使用另一种启用方法、该方法还提供软启动。 这是我很快将通过电子邮件向您发送的内容。

此致、

涉水