你(们)好

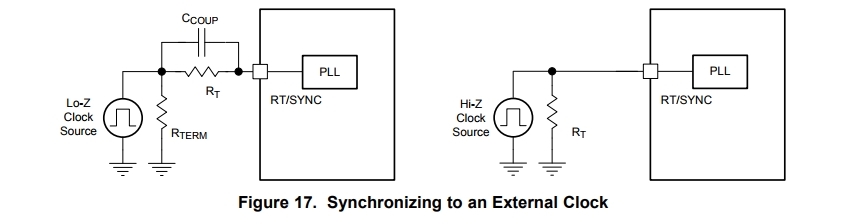

我对外部同步配置有一些疑问。

问题1:Rterm 为什么需要? 它涉及什么?

Q2:内部频率和外部同步频率之间是否存在任何关系或约束条件?

即 FREQ (RT)= 2MHz、SYNC FREQ = 450kHz。 这是可行的吗? 我们的客户希望使用500kHz 的外部时钟。

我们应该通过 RT 设置多少内部频率?

Q3:使用以下公式计算 Rterm。

Rterm= N *输入时钟电压/信号源电流。 (如果 LMR140xx 大于2、则 N 是 Rterm 的数。)

Q4:如果使用上述公式计算得出的 Rterm 值为9.9k、那么我们是否应该将 Rterm 设置为大于9.9k 或小于9.9k Ω?

Q5:如果用于 LMR140xx 的外部时钟连接到其他器件(不是 LMR140xx)、我们是否应该考虑器件时钟引脚的输入阻抗?

Q6:如果时钟信号源(MUC 等) 是推挽输出类型、电流定义为最大电流 (灌电流/拉电流)。 我们是否需要使用它的最小电流进行计算? (不是最大电流)

此致、

本志本