您好!

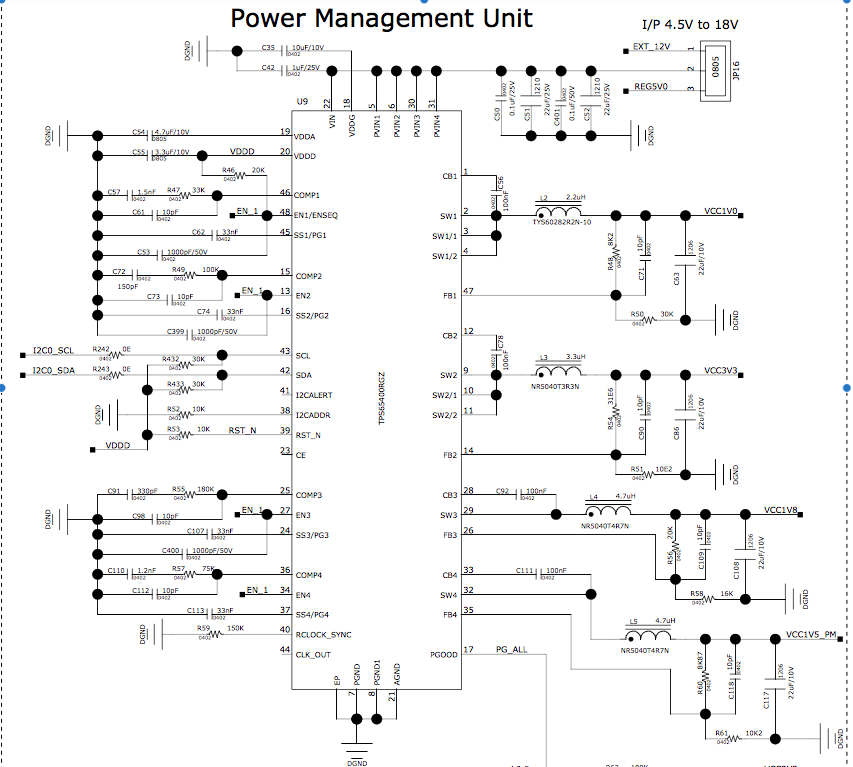

我在 FPGA 板中使用 TPS65400 PMIC。 原理图随附。 它与 ArtyZ7电路板中的"勤奋"使用的电路类似。

我发现 SW3的输出错误。 输出为3.3V、而根据连接的电阻器、输出应为1.8V。

其他三个输出是正确的。 这看起来很奇怪! 有什么想法、可能会出什么问题?

我测量的使能信号为1.6V、而它们实际上已上拉至等于3.3V 的 VDDD。

在 ArtyZ7电路板中、我测量到使能信号为2.7V、而这些信号实际上被上拉至3.3V (但不是 VDDD)。

在数据表中、我发现使能引脚上的1.28V 被视为高电平。 启用 PMIC 的正确方法是什么?为什么存在明显的压降?

更重要的是、为什么只有 SW3提供错误的输出?

谢谢、

Rajat Rao