大家好、

我不确定如何为 TPS544B25使用的补偿电路选择 FCO 值。我已在网上阅读、它应该是 FSW/10或 FSW/5。您能否告诉我们、选择用于稳定环路补偿电路的 FCO 和相补角的经验法则是什么。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

相位裕度为45-60度的 FSW/10和 FSW/5之间的差异将是一般经验法则。

fsw / 10通常较为保守、能够耐受布局电阻和电感等寄生效应 、而 fsw / 5较为激进、需要更加注意元件的实际 ESR。

此外、请注意在 L-C 谐振下出现的环路响应相位下降、尤其是在使用所有陶瓷输出电容器和低 DCR 电感器的设计中。 这些欠阻尼谐振系统的回路相位降非常低。 这不会导致稳态不稳定、但会导致输出电压在输出电压变化期间振荡、例如软启动期间或 AVS 的 VOUT_COMMAND 变化期间振荡。

如果您在 L-C 谐振频率下看到环路相位下降到35度以下、 我建议使用"设置极点和零点"频率选项并调整零点频率、以便第一个零点为 L-C 谐振频率的1/2、第二个零点约为 L-C 谐振频率的90%、从而在 L-C 谐振之前获得更多的相位升压。

或者、您可以手动将 C3加倍、这样可以将其零点频率降低1/2、而不会将增益改变为高于零点频率或极点频率。

我们如何在 Excel 工作表或图表中查看此内容?

我曾尝试对 TPS544B25网页上提供的 TI PSPICE 模型进行仿真。我看到 VOUT 上的纹波和开关节点上的脉冲跳跃。我可能知道这是建模问题、或者其他一些问题会影响仿真。

注-启动模型工作正常。

您好、Rajat、

我将介绍 Tahar 和 Peter、因为他们今天是 OOO。

我从 TI 网站下载了 PSPICE 模型、并且能够运行瞬态负载仿真、而不会出现任何问题:

虽然您说您尚未更改 TI 默认值、但您的仿真结果中的负载阶跃已更改。 例如、TI 默认具有20A 负载阶跃、但您的负载阶跃为10A。

您是否有任何其他更改、以便我们最终可以复制它?

谢谢、

Tomoya

此外、请注意在 L-C 谐振下出现的环路响应相位下降、尤其是在使用所有陶瓷输出电容器和低 DCR 电感器的设计中。 这些欠阻尼谐振系统的回路相位降非常低。 这不会导致稳态不稳定、但会导致输出电压在输出电压变化期间振荡、例如软启动期间或 AVS 的 VOUT_COMMAND 变化期间振荡。

如果您在 L-C 谐振频率下看到环路相位下降到35度以下、 我建议使用"设置极点和零点"频率选项并调整零点频率、以便第一个零点为 L-C 谐振频率的1/2、第二个零点约为 L-C 谐振频率的90%、从而在 L-C 谐振之前获得更多的相位升压。

如何检查?

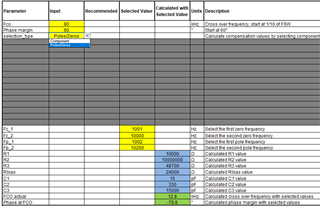

TPS544B25产品文件夹中提供的 TPS544B25 Excel 设计计算 器- www.ti.com/.../TPS544B25 包含预测波特图的图形表示。

通过选择低电感器 DCR、低电容 ESR 和低输出电流、您可以在 L-C 谐振时使相位快速下降、然后 III 类补偿的两个零可以升压相位。 要降低其中一个零点并在 L-C 谐振之前增加相位、而不增加环路带宽、请增大 C2的值

将 C2从820pF 增加到3900pF 可降低零点、并在 L-C 谐振之前提供所需的相位升压。

要将零极点频率选择用于补偿设计、请在电池 C89中为选择类型选择"零极点"。

在 fz_1 = 1/2 LC 谐振、fz_2 = 0.9x LC 谐振、fp_1 = ESR 零点频率或1/2开关频率的较低值、fp_2 =开关频率的指导下运行。

我们可以看到、即使在我们在此遵循的极端条件下、在 L-C 谐振下、相位也保持在接近45度的水平

是的、F_LC 是 L-C 功率级的谐振频率。

是的、您应该检查"总系统波特图"图、希望是从 VOUT 进入反馈到电感器输出 VOUT 的完整电压调节环路。

它并不是我们所关注的谐振频率、而是相位图的谷值、它将稍微高于谐振频率-在上面的示例中大约为13k。

对于这个特定的测试、我想将 IO 设定为电感纹波峰峰值的1/2 -也被称为临界导通、因为这是负载电流、即 L-C 谐振阻尼最低、而共振相移最差。

35度不是"硬性"规则、而是一般经验法则。 当环路在该频率下需要高增益时、L-C 谐振下的较低相位裕度往往会导致输出电压在该频率下振荡、例如跟踪由于 VOUT_COMMAND 中软启动或 AVS 变化而导致的基准电压变化、 或从大型负载瞬态恢复期间的瞬态响应。