Thread 中讨论的其他器件: TIDA-00778、鳄鱼

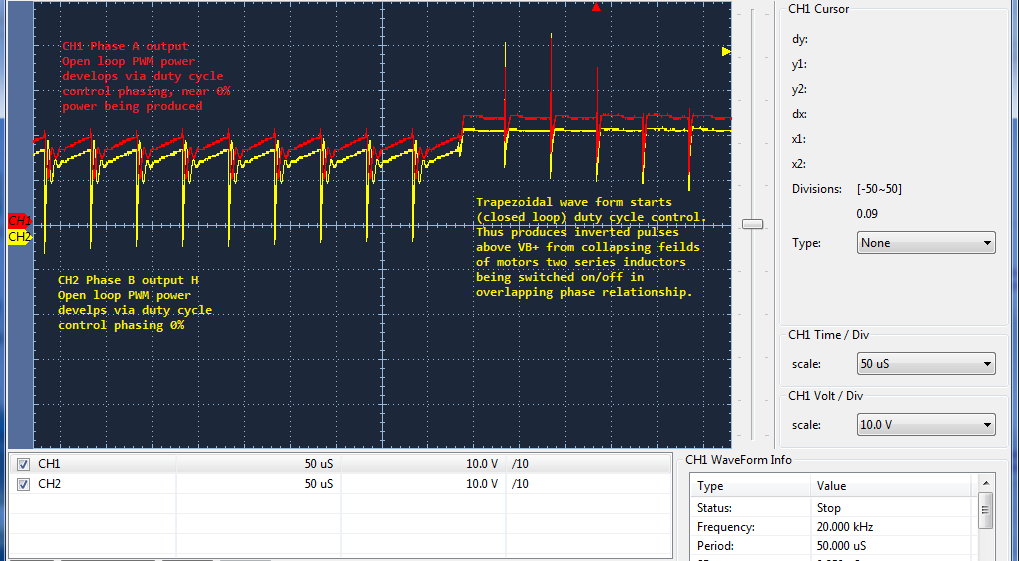

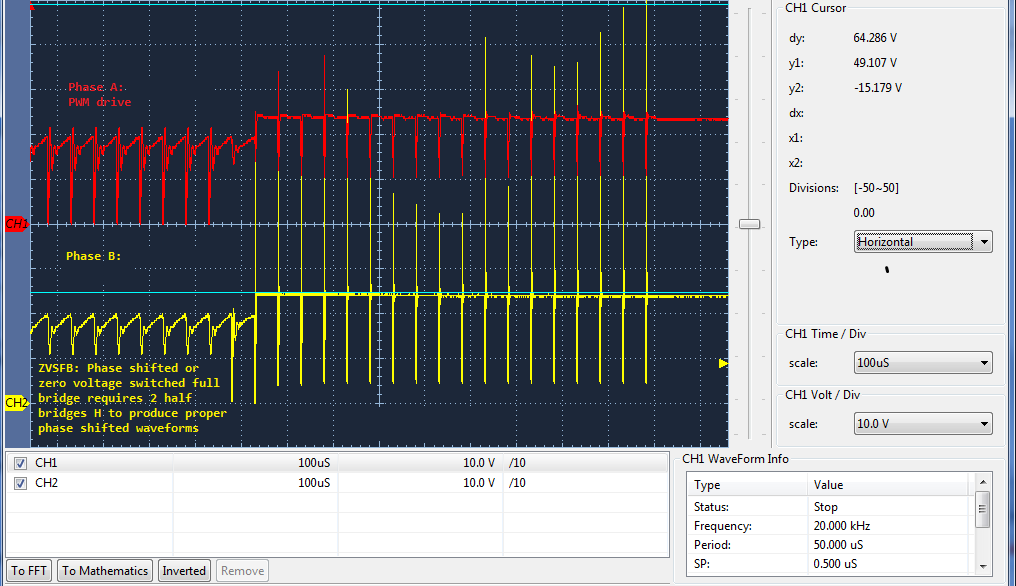

由于 HI/LI 被 UCC 单独延迟40ns、因此我们似乎无法从 MCU 驱动的 PWM 发生器中持续产生低于或高于1us 的适当看起来脉冲宽度。

以前的系统 栅极驱动器仅 在 LO 输入上插入了延迟匹 配、并通过 LO/HO 在 LI/HI 上产生了接近100%占空比的8-80Khz PWM。 这是一项共同的工作、需要在 合作伙伴现场阶段划分中使用两个 UCC 栅极驱动器和两个同步 PWM 发生器、然后再滚动到第三个 UCC 以实现三相换向方案。 A-B、A-C、B-A、B-C、B-A、 C-A 合作伙伴硬开关 半桥架构需要6个代码来驱动逆变器。

UCC 通过 将 LI 和 HI 输入分别延迟 40ns 来 保持与 TM4C1294XL PWM 外设发生器在合作伙伴阶段的兼容性吗? 从这一点开始、40ns 延迟匹配似乎阻碍了合作伙伴栅极驱动器的正确脉冲生成。 当要求共伙伴栅极驱动器的 HO/LO 都产生此类脉冲时、1/2 脉冲生成 通常是 MIA 或在电源轨以上反相、并非总是、而是比预期的频率更频繁。

直流逆变 器似乎始终与 PWM 发生器保持同步、并在该过程中产生非常失真的脉冲和宽度。 即使在 每个 周期结束时不产生反相脉冲的 HO 合作伙伴 也会失真、并且不会降至 1/2 Vs。