主题中讨论的其他器件: UC1825、

在低占空比下运行时、UC3825出现了一些问题。 此器件控制一个对称半桥转换器、振荡器被设定为380kHz、LEB 被设定为最小值(通过将一个没有任何电容器的2k15连接至 LEB 输入)。 斜坡输入由斜坡补偿信号和少量变压器初级电流(峰值电流模式)馈送。 未使用软启动(引脚 o/c)和 ILIM -功能(电压<200mV)。

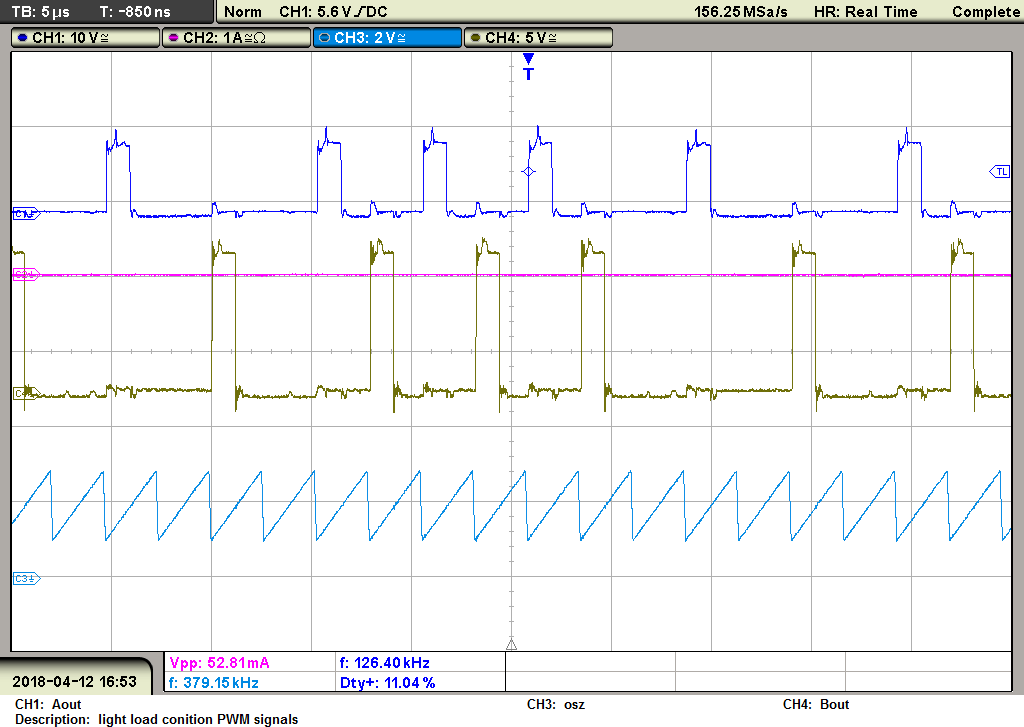

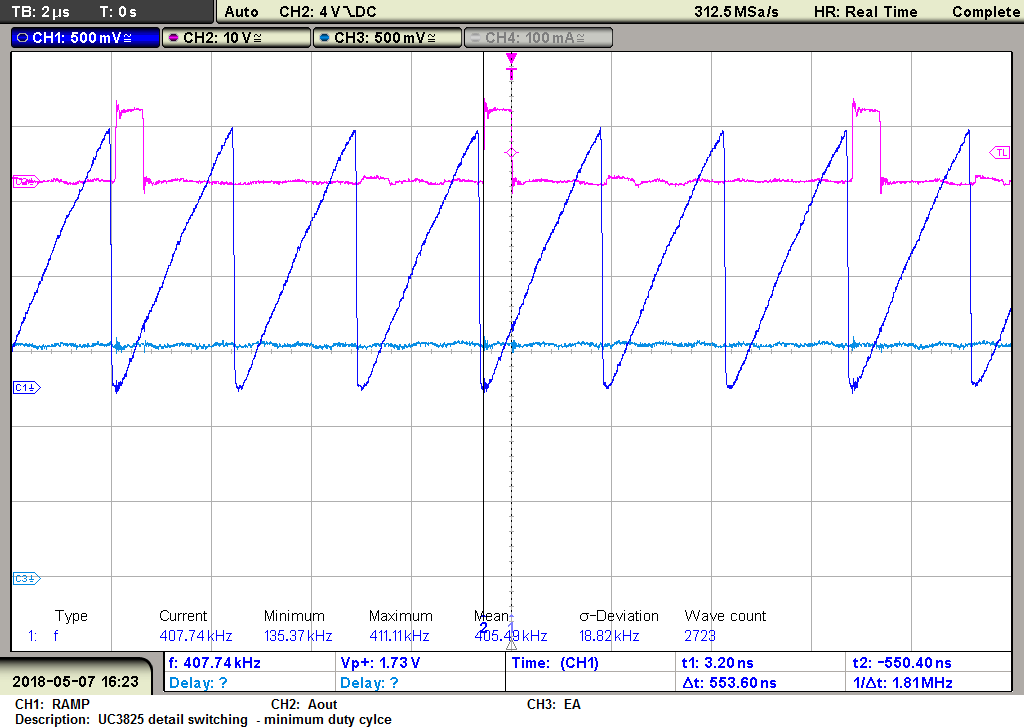

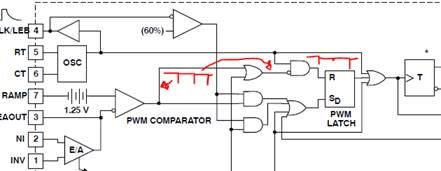

该器件在中高负载条件下按预期运行、其中转换器在连续导通模式下运行(每个输出的占空比约为30%)。 在轻负载条件下、会发生非连续导通模式、并且占空比会降低。 在这种情况下、最小占空比残桩约为20%。 如果需要较低占空比的时钟、Aout 或 BOUT 输出上的一些脉冲将被完全抑制。 内部切换触发器看起来也是以非二进制方式切换。 这种影响还会导致可闻噪声、因为施加到变压器初级的交流电压会受到干扰。

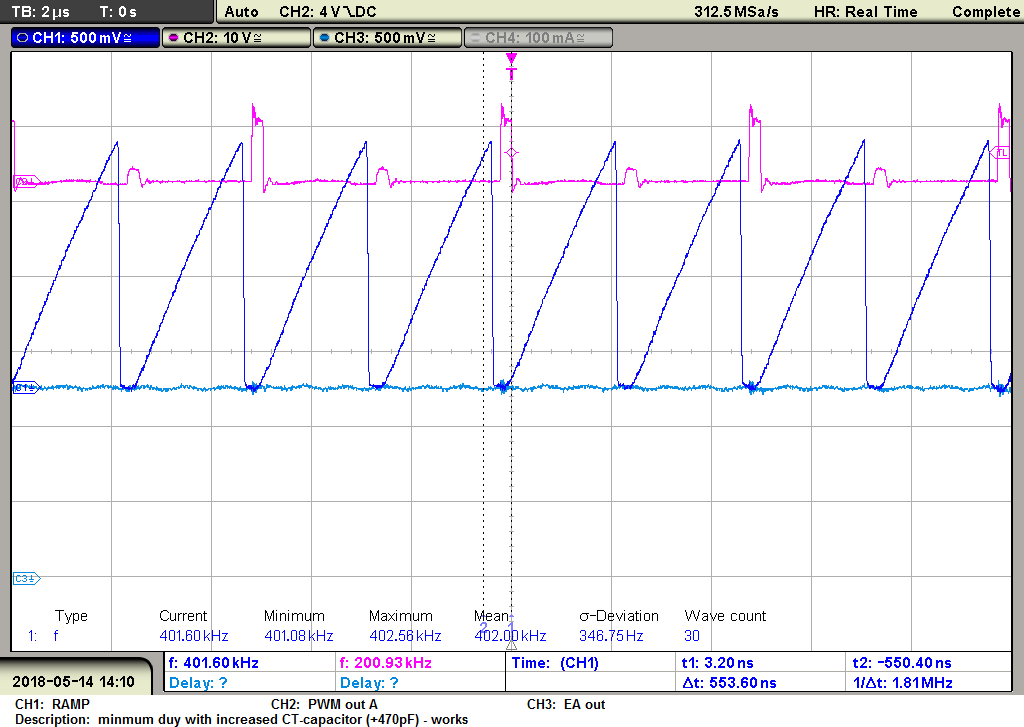

下面是一个典型测量值:

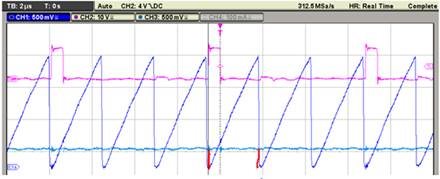

我已通过连接 CT 和斜坡输入来应用纯电压模式(如数据表/APP 注释中所示)来修改电路:已达到相同的效果但占空比略低。

我还通过屏蔽和过滤电源和其他信号来减少各种 EMC 影响->无影响。

通过减小施加到斜坡输入 端的三角信号的源阻抗、已达到较低的最小占空比-但效果仍然可见。

数据表未提供任何有关最小占空比的信息(文本中规定可实现零占空比);也未提供有关斜坡输入所需源阻抗的信息。

这种影响是否已知? 是否有工作安排?

我们目前使用 UC3825作为试验电路板-但我们希望使用 UC1825作为产品。 UC1825的情况是否相同?