您好!

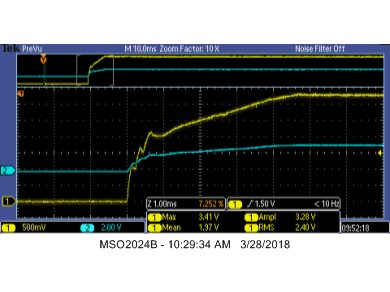

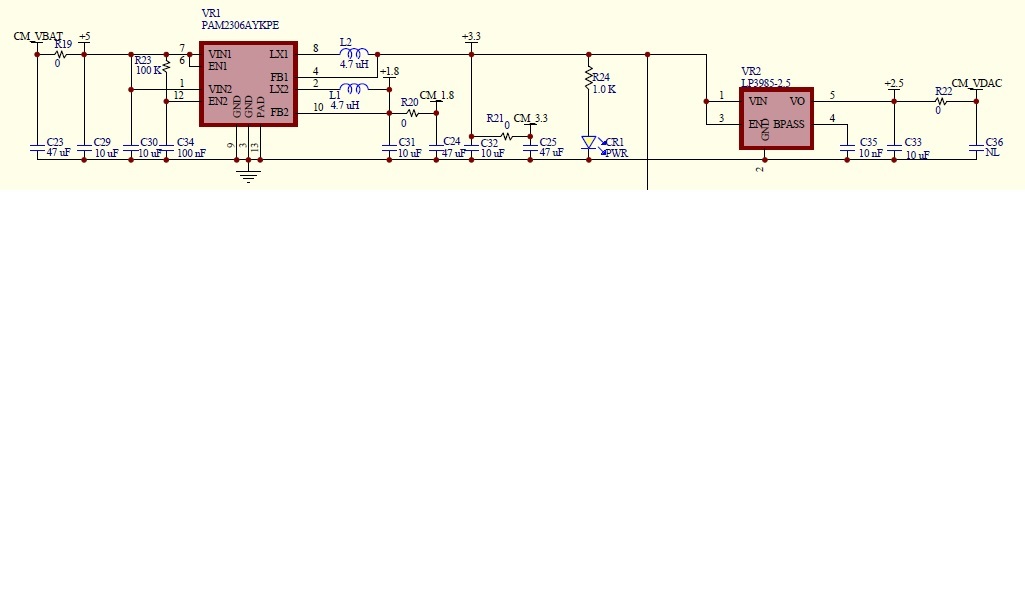

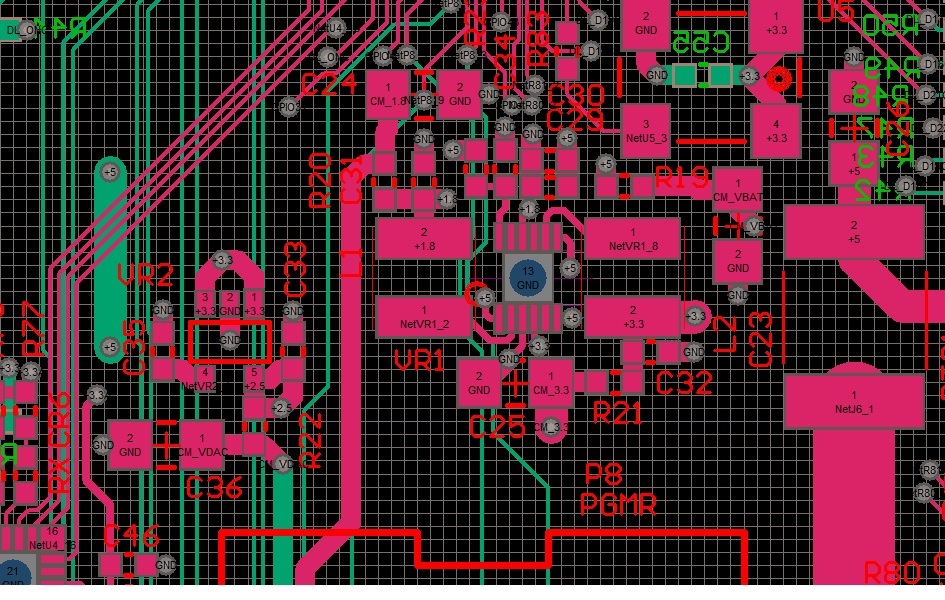

我正在调试一个使用 LP3985-2.5为 FPGA 供电的新设计。 同一 FPGA 还具有在3.3V 上运行的组。 我在稳压器和 FPGA 之间有一个0欧姆串联电阻、因此我可以断开 FPGA 负载、只留下输出电容器。 LP 的输入端有10uF 与47uF 并联、其输出端有10uF。 旁路和接地之间有一个10nF 的电容。 我有两个原型板。 最初、3.3V 和2.5V 之间似乎存在短路(当然在 FPGA 下)。 我移除并更换了 FPGA、短路消失了、但我使用的是相同的 LP3985-2.5。 由于其输出现在已从 FPGA 断开、但仍连接到其输出电容器、LP 输入测量3.359V、其输出测量为3.216V。 我有另一个板、其 LP3985输出最初连接到 FPGA 并测量3.3V 电压、因此我移除了其零欧姆跳线。 第二块板的 LP3985-2.5从其负载上断开、测量值为3.24V、输入为3.28。

因此、在第一个电路板上、LP 的输出可能会被拖至高于其标称2.5V 输出值。 从简化的方框图中可以看出、这似乎不会损坏 LP、因为如果输出被拉至其调节值以上、它将无法灌入电流。 然而、在第二个电路板上、存在(并且从未)短路、因此很难解释它如何不再进行调节。 我已附上原理图。

任何想法都值得赞赏。

谢谢、

Scott