尊敬的专家:

我们遇到了 TPS65217C 上电问题。 我们可以在为 VBAT (3.6V)或 AC (5V)供电后测量正确的 SYS 电压。

我们按照要求将 SYS 连接到 VIN_LDO。 从数据表中可以看出、LDO1电压应与 SYS 电压直接输出、但我们无法测量该电压。 (VLDO1上没有负载)

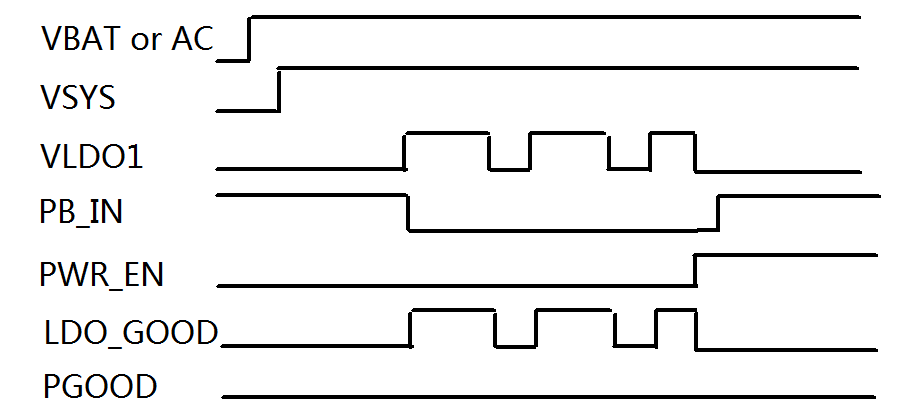

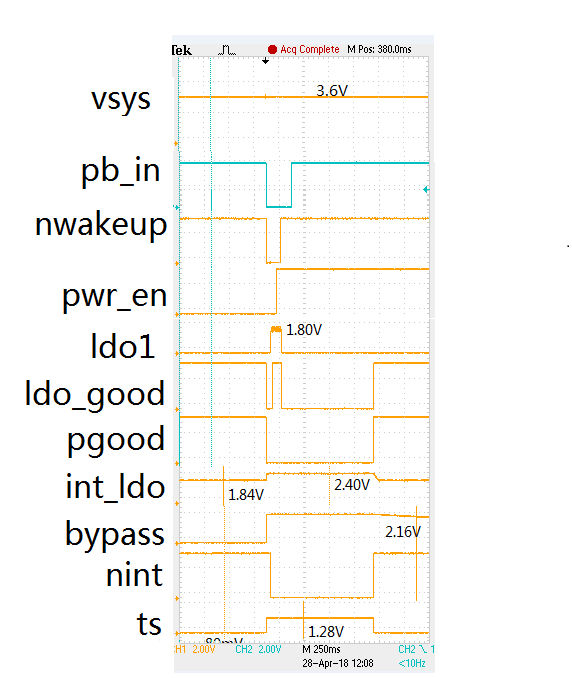

当我们将 PB_IN 保持为低电平时、我们看到5s + 3s 周期、看起来类似于"Wait PWR_EN timeout"和"PB_IN reset":

-in 5s period -> LDO1输出为1.8V、LDO_GOOD 为高电平、PGOOD 为低电平。

-in 3s period -> LDO1输出为0V、LDO_GOOD 为低电平、PGOOD 为低电平。

-一旦我们将 PWR_EN 拉为高电平、LDO1输出就会降至0V。

-如果我们将 PB_IN 拉为高电平、在这5s 周期之后、LDO1输出下降至0V、永远不会回到1.8V。

您能为我们提供这方面的帮助吗?如果您需要额外的信息或实验、请告知我们。 非常感谢。