主题中讨论的其他器件:TPS43351-Q1

您好!

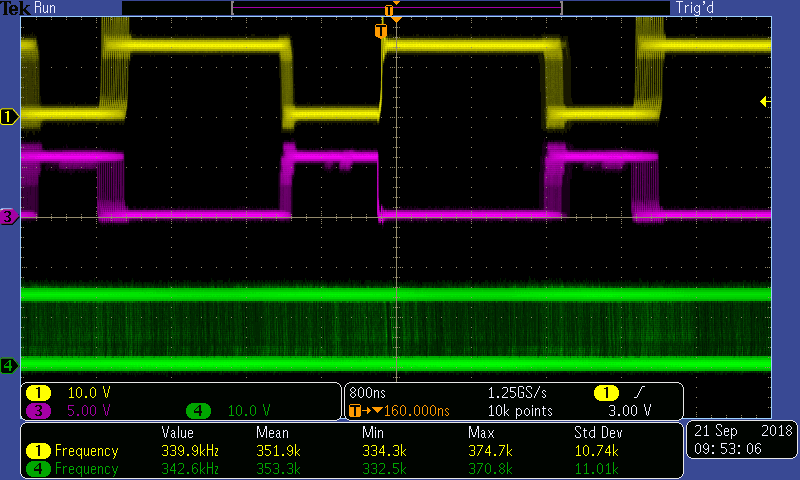

我现在提出这个问题是因为我想确保频率同步问题没有故障。 现在这些问题已经解决、我有了相同的电路、现在输出#4、Gorion 具有完整的原理图。 对于高于12.0V 的 VIN 和高于3.5A 的 Iout、我看到开关节点占空比中的次谐波干扰逐渐变差。 增大 VIN 和/或 Iout 会使该振荡变得越来越明显。

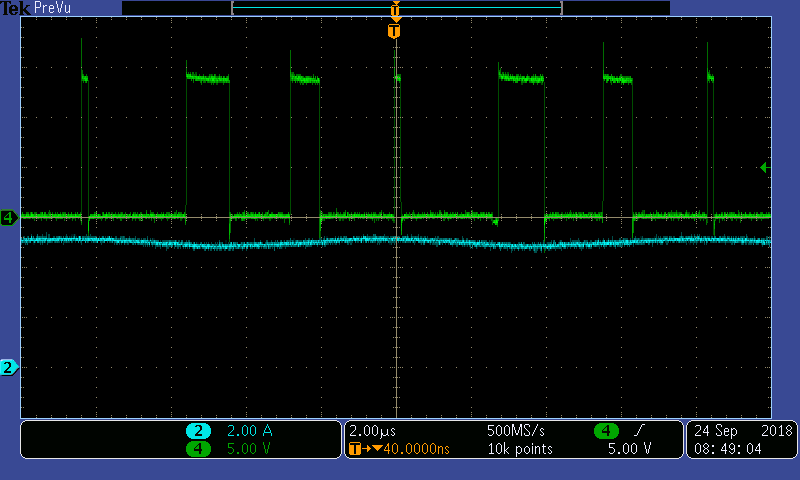

通道2 = Iout、通道4 = SW 节点、这是针对 VIN = 13.8V 和 Iout = 5A (最大负载)

我关于该 IC 的第一篇文章导致了电路板上第一个 TPS43351-Q1的两处变化、即移除连接另一个输出为5.0V 的电阻器到 EXTSUP 引脚、并将 VREG 引脚电容增加到4.7uF。 我已经对第二个 TPS43351进行了这两个更改、该更改可生成3.3V、5A 输出、但这两个更改都没有停止振荡。

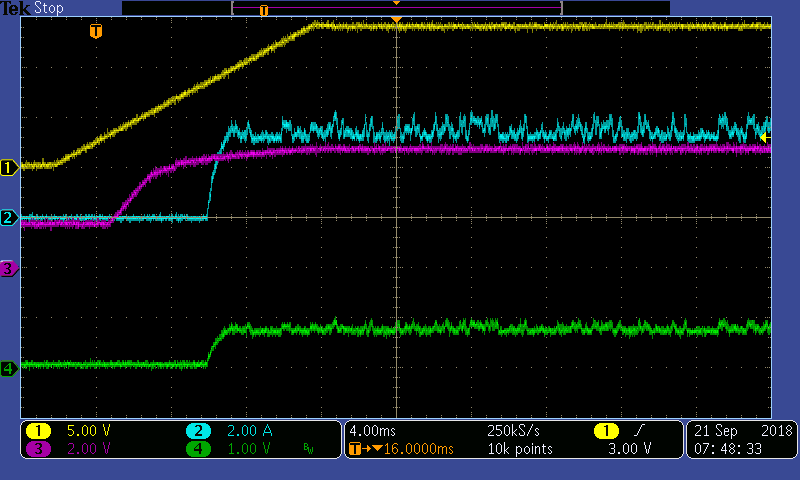

此外、我发现、如果我尝试通过施加输入功率或使用逻辑使能来启动高于3.5A 的负载(恒定电流负载)、则输出将卡在大约0.8V 的电压下、并提供3.5A 的平均电流。 以下是此类启动的图解:

通道1 = VIN、通道2 = Iout、通道3 = ENA 和 ENB 引脚、通道4 = Vout

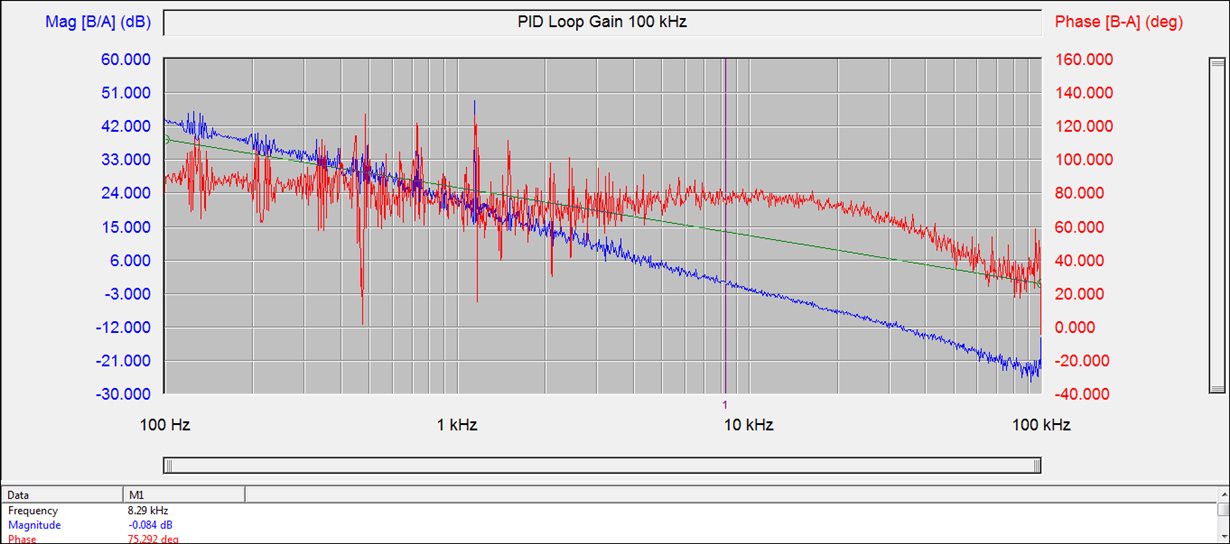

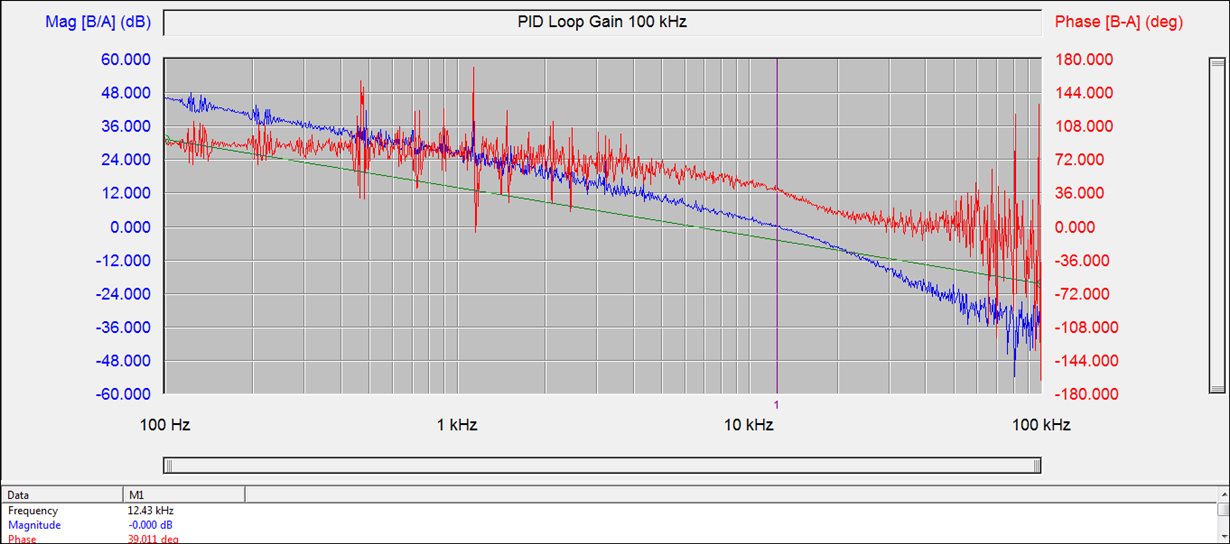

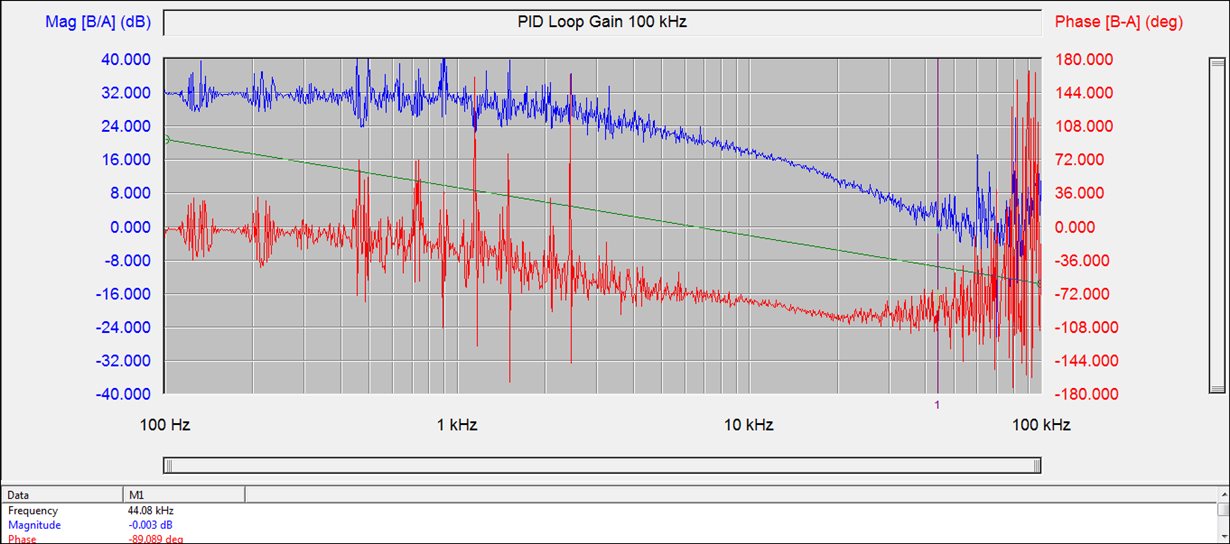

解决此问题的方法是降低电流感应电阻。 为了实现相当平稳的单调启动、我必须将电流感应电阻从原来的5 m Ω 降低到2.5 m Ω。 这会导致增益相位响应发生一些变化、因此我还调整了控制环路补偿。 这是保守但非常稳定的:

在对相位裕度存在一些混淆之前-这是直接读取的、并在底部报告:8.3 kHz 带宽时为75º μ W。 这是在 VIN = 13.8V 且 Iout = 3.0A 的情况下进行的。 高于3.5A 时、波特图只是噪声。

我排除了输入端的电源阻抗相互作用、主要是因为当 VIN 下降时、这种不稳定实际上会变得更好-与您在输入阻抗导致问题时看到的情况相反。 我已经排除了控制环路中的低相位裕度或增益裕度。 我不想进一步降低电流感应电阻、因为我担心信噪比。 还有什么可能导致次谐波振荡?

谢谢、

Chris