Other Parts Discussed in Thread: UCC28740, TL431

Thread 中讨论的其他器件: TL431

您好!

我正在使用 UCC28740进行电源的新迭代、但无法使其正常运行。

在上一次迭代和本迭代之间、我主要将最大输出电流从2.1A 降低到0.9A。

我使用计算电子表格、根据变压器(以及 CS、VS 和 FB 引脚周围的电阻器)的主要差异。

新转信息生成的样本已经过测试、符合电子表格值的规格。 旧的转速是由另一家公司制造的、我不确定它们是否符合规格。

我将缓冲器 TVS 更改为超快速瞬时 TVS (TRR 从500ns 变为75ns)。

我还添加了一些额外的 EMI 缓解元件(交流输入上的第二个共模扼流圈用于滤除50至500MHz 之间的辐射噪声)、并在缓冲器中添加了铁氧体层以消除一些高于500MHz 的峰值。

这两个应用于旧电路板的修改都不影响功能、从该电路板上移除这些修改不会使我的问题得到更好的解决。

在 TI FAE (较大的 RLS、调整的 F3/F4和变压器匝数 IIRC)对计算表进行了一些更改之后、之前的版本正常工作(与我可以检测到的预期行为没有偏差)。

很遗憾,我不能说我理解了这里的所有细节(他只讲中文),我不能再回去了。

输入电压:85至245VAC、输出5.6V @ 0.9A

原理图(我没有展示制造 VBLK 的器件、它是标准器件、VBLK 是稳定的。

计算表 attached.e2e.ti.com/.../UCC28740-design-calculator-_2800_5.6V_4000_0.9A_2900_.xlsx

在这个新版本中、我有两种情况:

1) 1)如果我将一切如计算表中所示(或靠近计算表 CF "实际值")、则芯片启动、获得略高于 VOUT_CV (但低于 Vout_OVP)的 VOUT、然后停止。

2) 2)如果我移除电容器 CZ (在原理图中、TL431基准的阴极和 REF 之间的电容器 CZ)、则电路板会运行、在适当的电压下提供稳定的输出、在负载上表现良好、但开关模式错误、从而导致输出上产生过多纹波。

在这两种情况下、VBLK 均正常、由于大容量电容器略大、且电压约为300-310V、因此非常稳定。

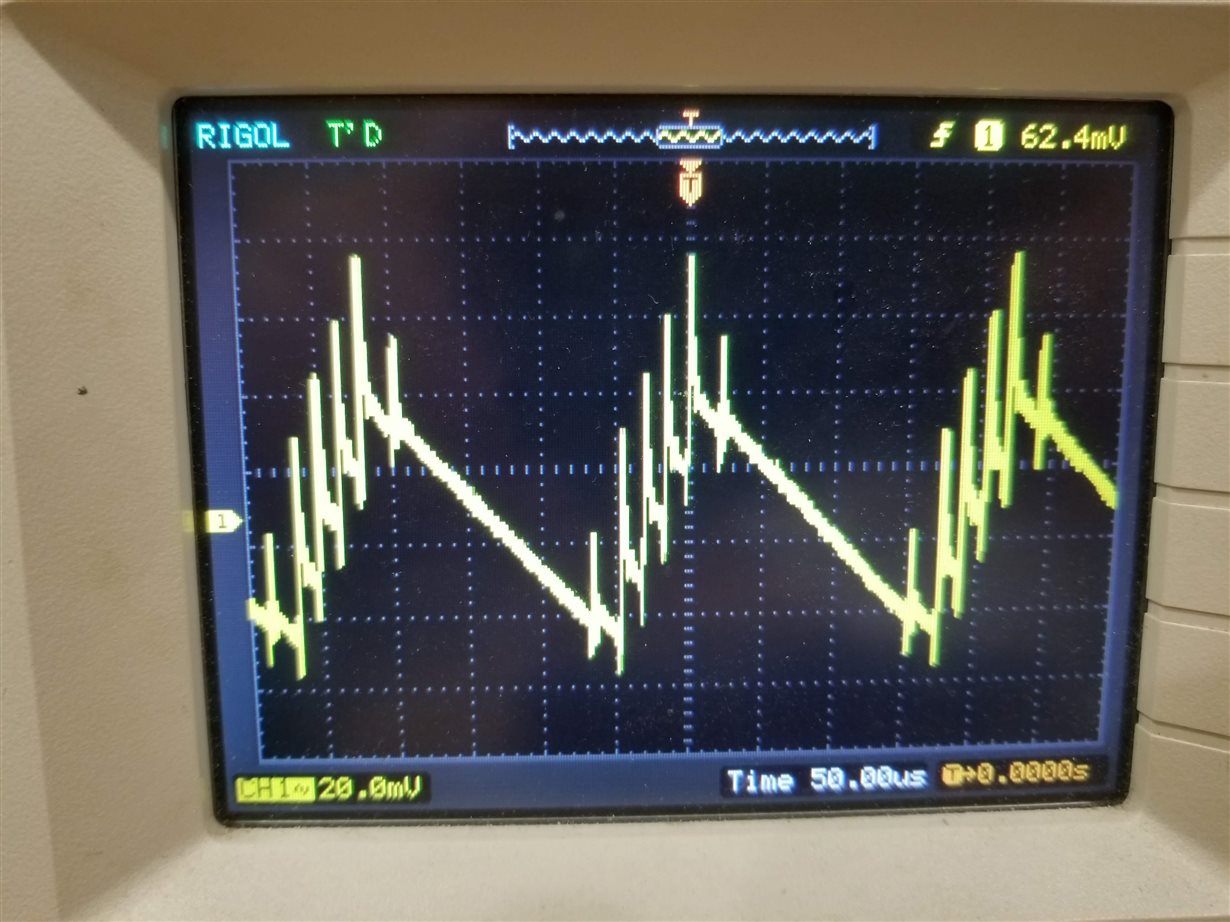

我测量了谐振周期、看起来太长:大约2.5us、而 Tzto 只有2.1us。

数据表和故障排除指南中的该部分不清楚、因为简单地说、该周期应低于 Tzto、因为担心缺少某些谷底开关、而不是可能阻止所有器件运行。

我在这里和那里看到了非常少的山谷,如果仅仅是效率,我现在还可以使用它。

应用谐振周期公式("TI PSR 控制器故障排除"的6.1)、了解变压器初级侧的实际电感后、我得到一个 CSW、当计算表中的输入返回一个非常不同(较短)的周期时、这在这里是有点不正确的。 如果该计算结果良好、那么当我更改 MOSFET 以便 Coss 从53pF 变为28pF 时、周期应该可以测量地降低、但它保持不变、正如我所能说的。

降低电感将是我要寻找的结果、我无法控制其他参数...

有关每个案例的更多详细信息:

1)

当 VDD 超过导通 UVLO 阈值时、芯片启动、然后它会切换、直到输出电压略高于预期输出电压、然后它会停止开关、这似乎是由于 CS 过压造成的。

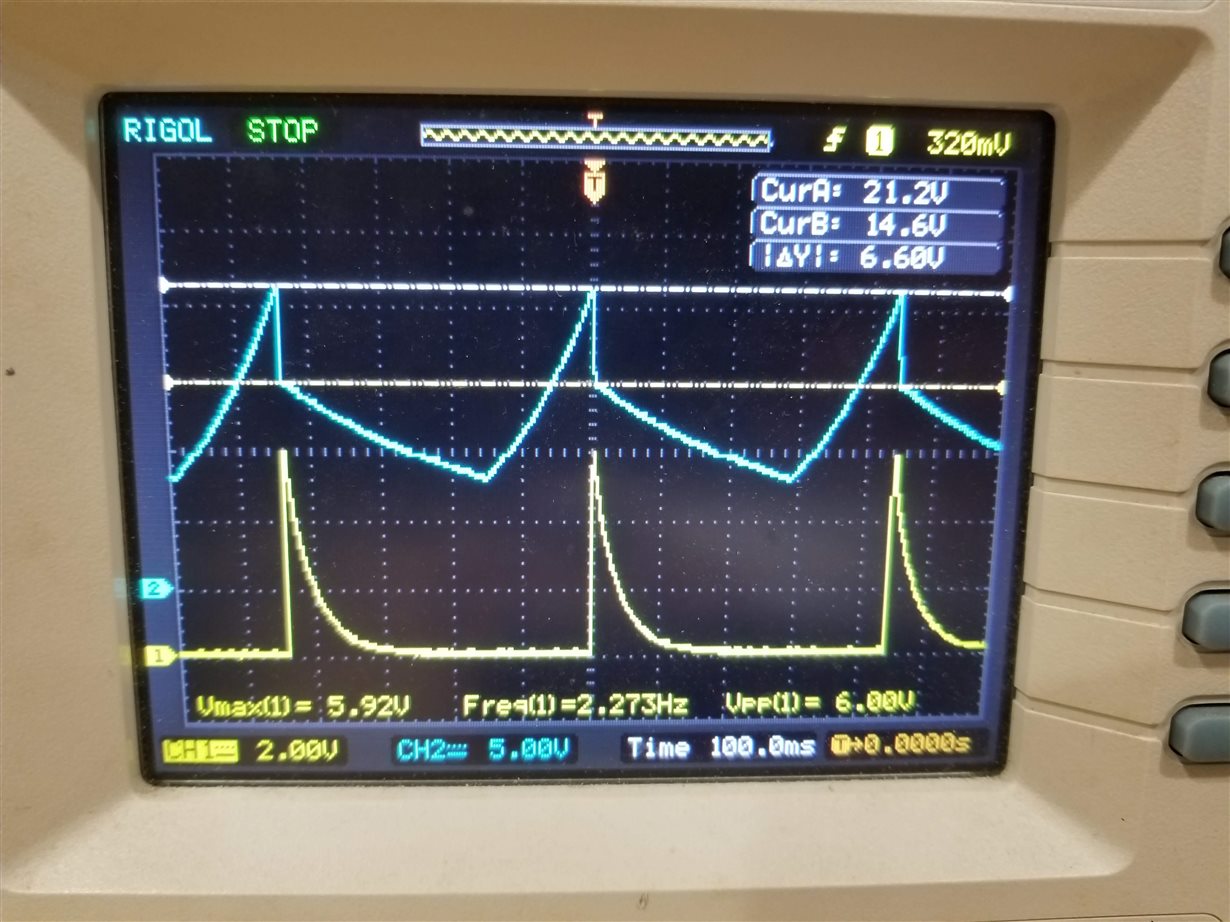

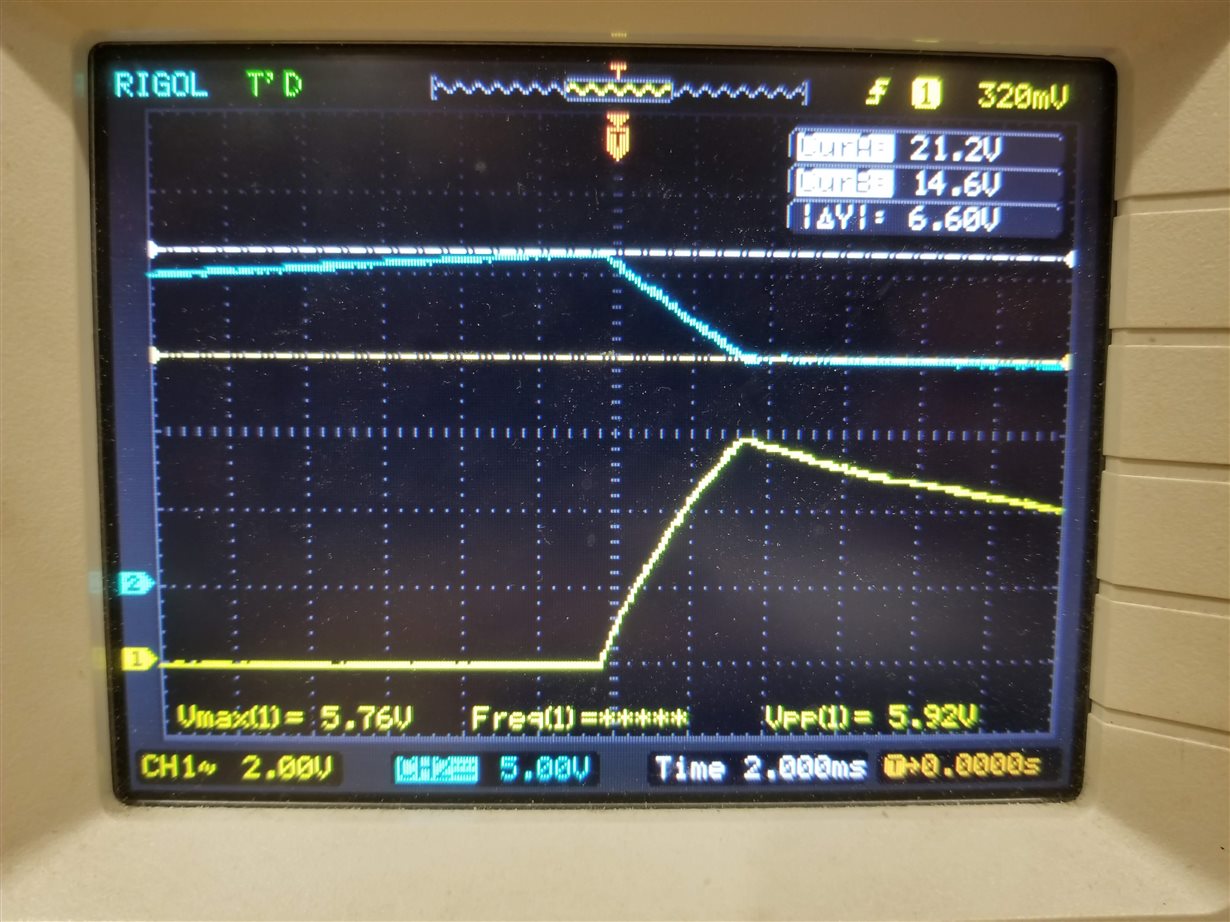

此时 VDD 从21V 变为约14.6V、然后在开始另一个周期之前缓慢向下漂移至关断 UVLO 值。

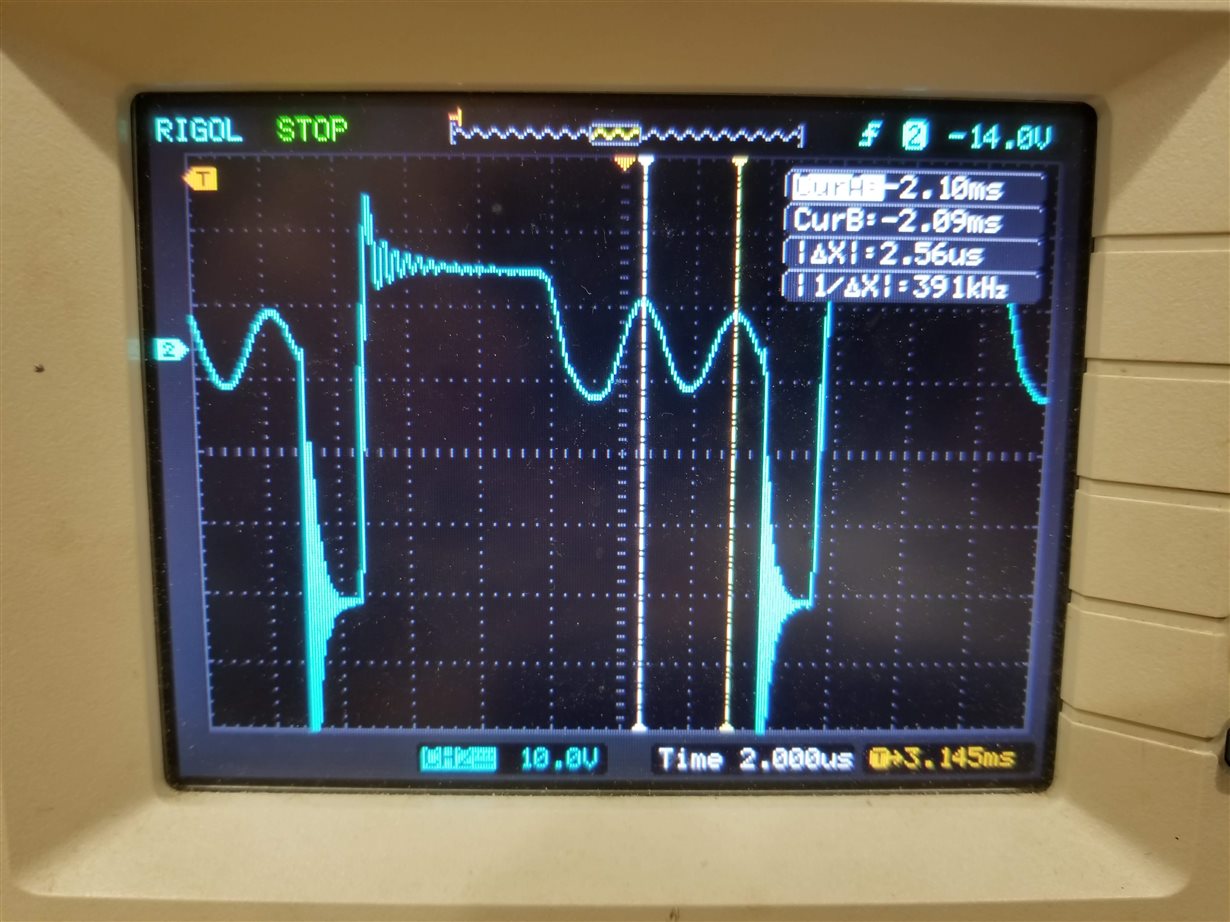

CH1:Vout、CH2:VDD。 显示了多个周期。 芯片停止切换后、VDD 缓慢下降、直至达到 VDD (off)并重新启动周期。

CH1:Vout、CH2:VDD。 在芯片运行期间放大了时间。

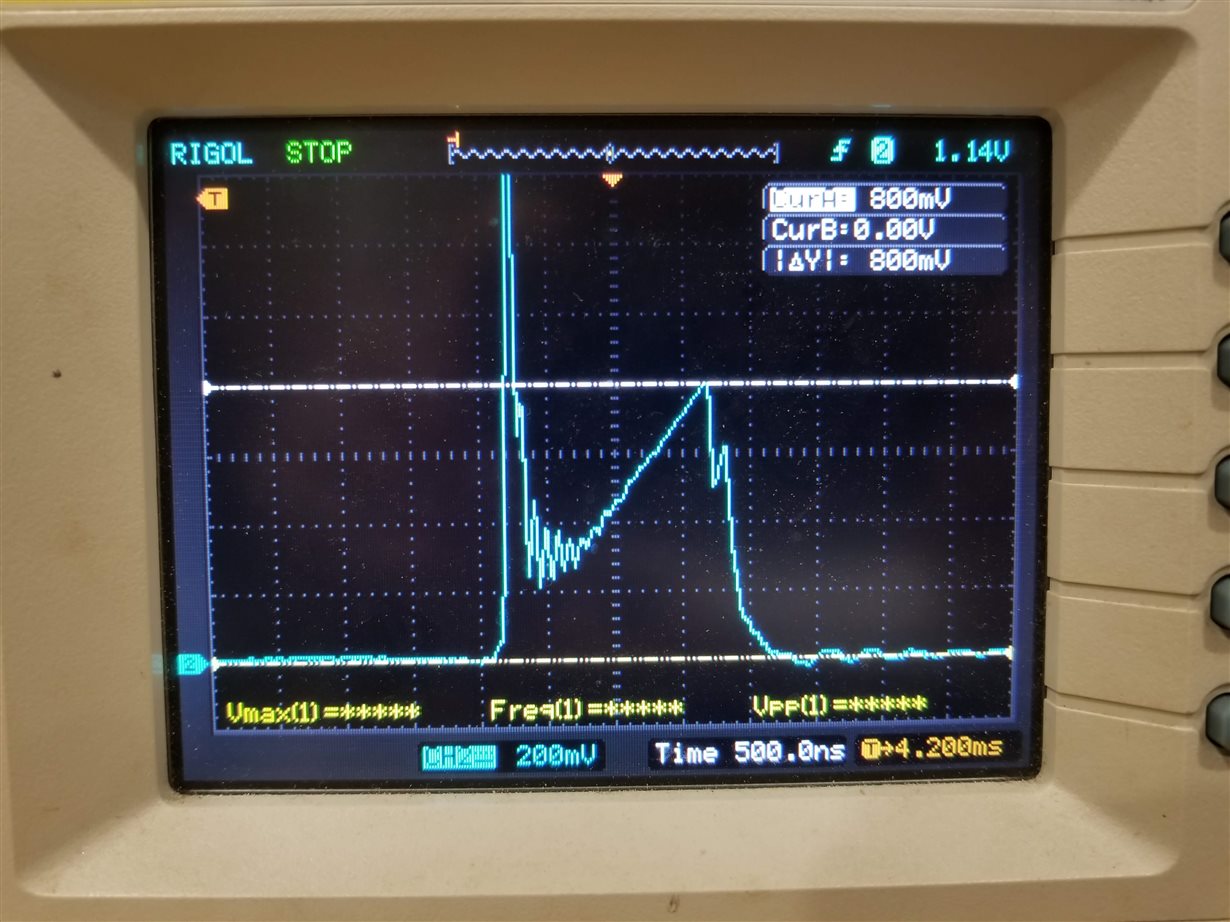

最后一个周期内 CS、VS 和 FB 的 PICS:

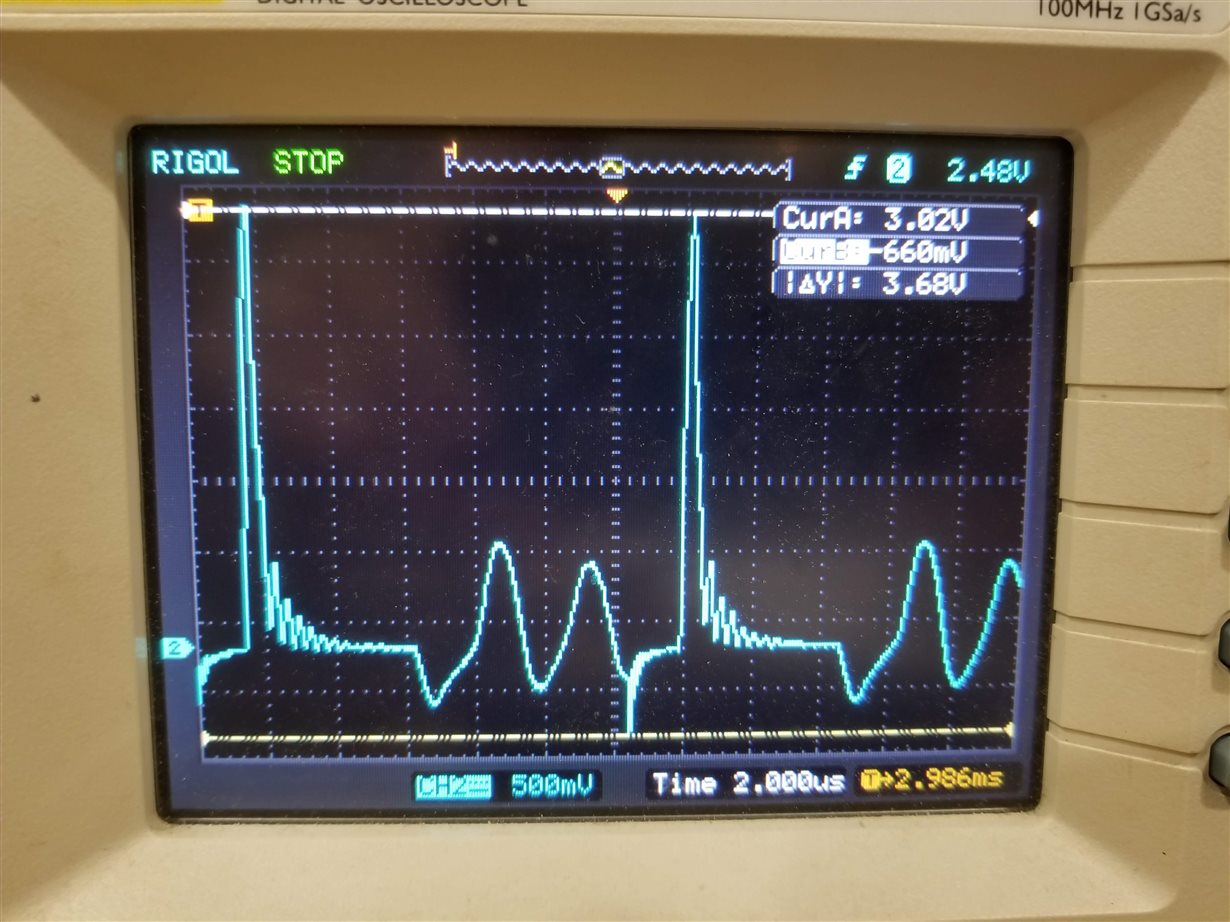

通道2:CS。 VCS 在最后一个开关周期高于 Vcst (max)。

CH2:Vs.在最后两个周期中、VS 上升至4.6V。

如果我更改 RCS 和/或 RLC 以降低 VCS、它仍将达到该值。 我尝试使用 RCS=1.6欧姆且 RLC=3.3K (而不是1.82k)、VOUT 在停止前上升到6V。

2)

在这种情况下、稳压(测量 RMS 时)良好、负载下的响应令人满意。

但是、芯片在某种突发模式下工作(不应该存在于此芯片中)。 它将以固定频率(约68kHz、低于理论最大开关频率)进行开关、而不是调节其频率以考虑负载、而是获得高于预期输出电压约150mV 的输出、然后停止、直到输出在预期输出电压下可能变为200mV。

产生的纹波取决于负载、但无负载时的开关频率相同、高达500mA (上面没有测试过 I)。

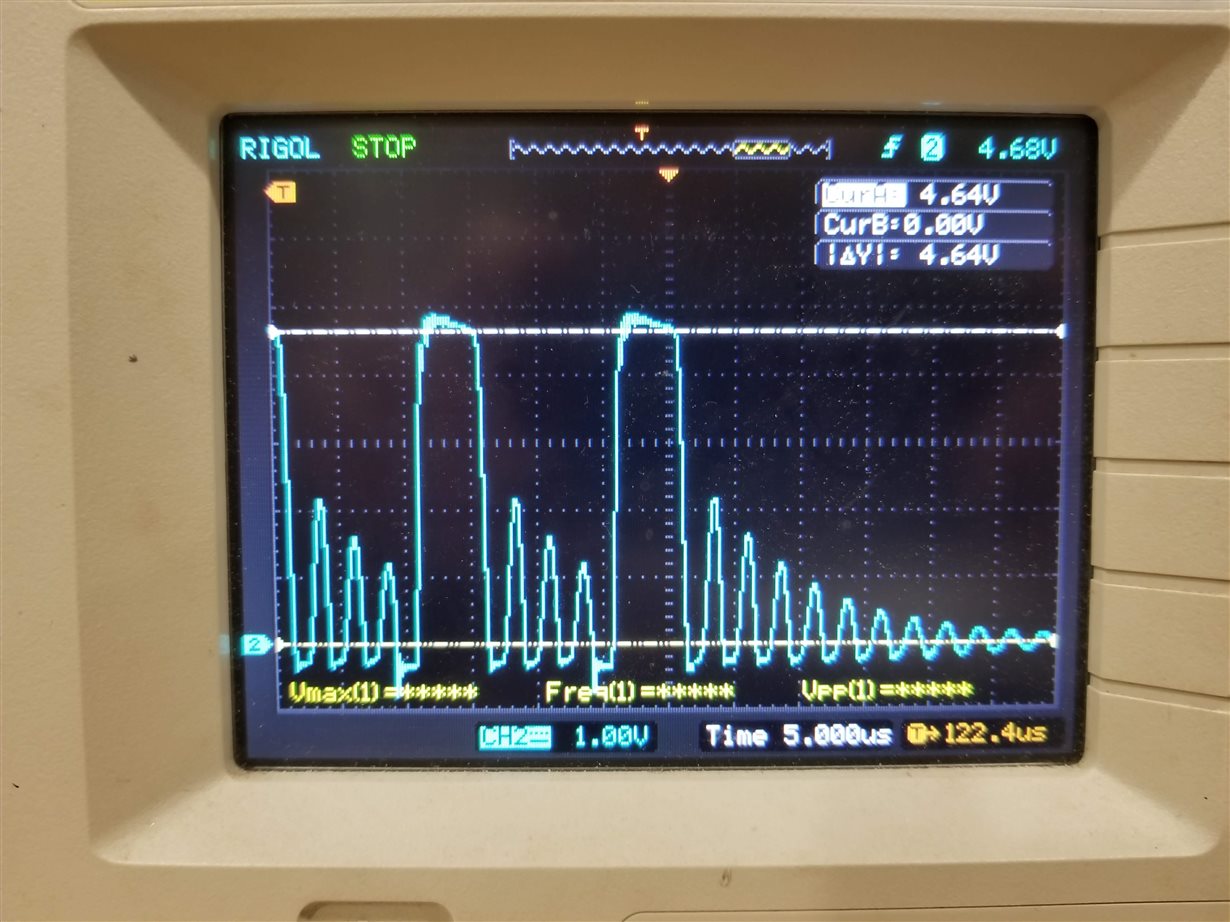

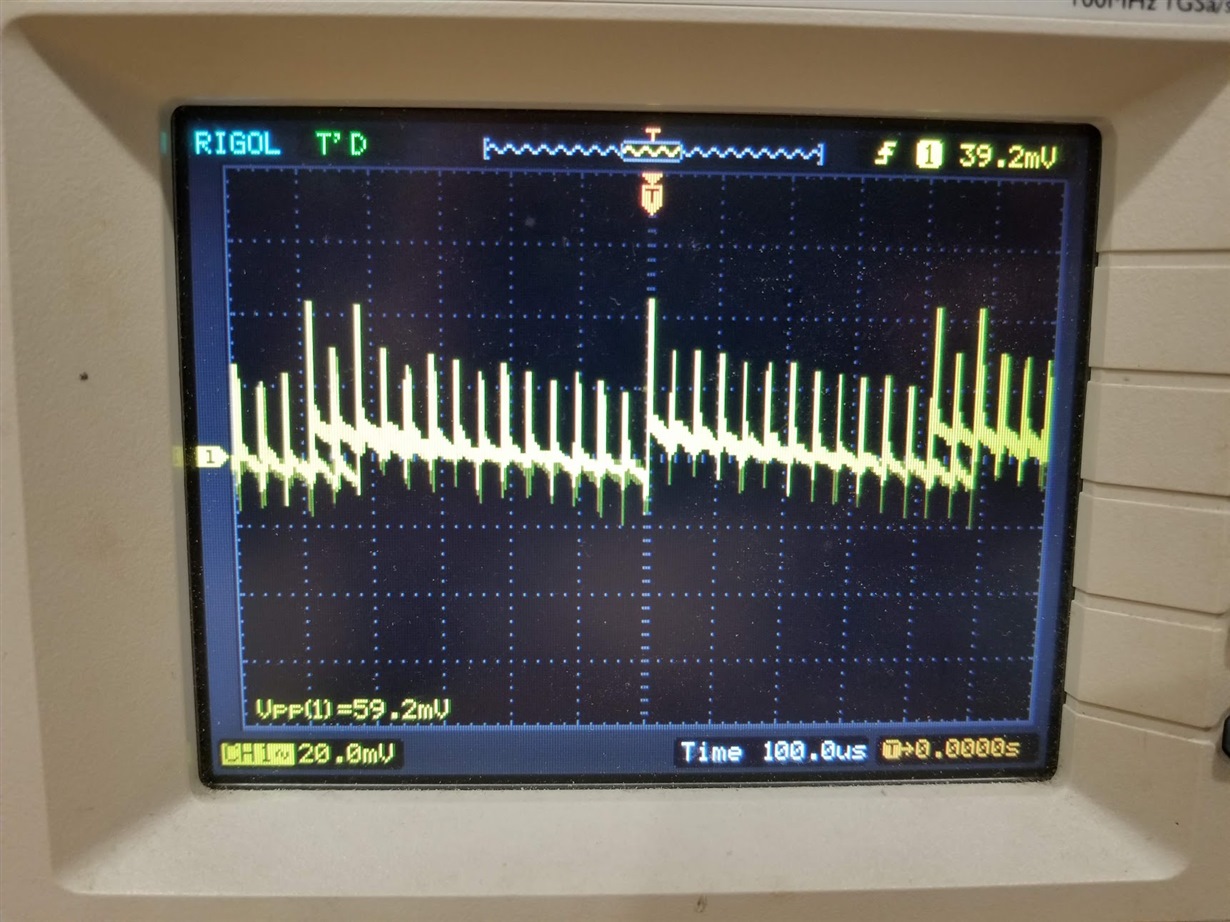

通道1:VOUT。 开关频率为30us (66.67kHz)。 下降斜率取决于负载、总纹波频率也是如此。

我已经在这方面工作了几天、我被骗了。 该文档中有足够的不清楚细节(经验丰富的电源设计人员可能不会对其产生任何疑问)、我不确定我是否正在取得进展、或者只是对我尝试的所有电阻器的所有变化失去了更多的了解...

顺便说一下、我组装了两块板、它们的行为都是一样的、就我可以检查所有组件而言、我认为它们都是一样的(我在组装之前重新测量了所有电阻器、以防万一、我之前曾让 Farnell 给我发送了错误的值...)

是否有什么想法正在发生什么以及如何取得进展?

提前感谢。