主题中讨论的其他器件:ADS54J60、

您好!

我使用4个 TPS7A8300为定制板上的 ADS54J60供电。 ADS54J60的要求之一是、在启动 DRVDD (1.9VD)之前启动 IOVDD (1.15V)、否则将无法正确加载默认寄存器值。

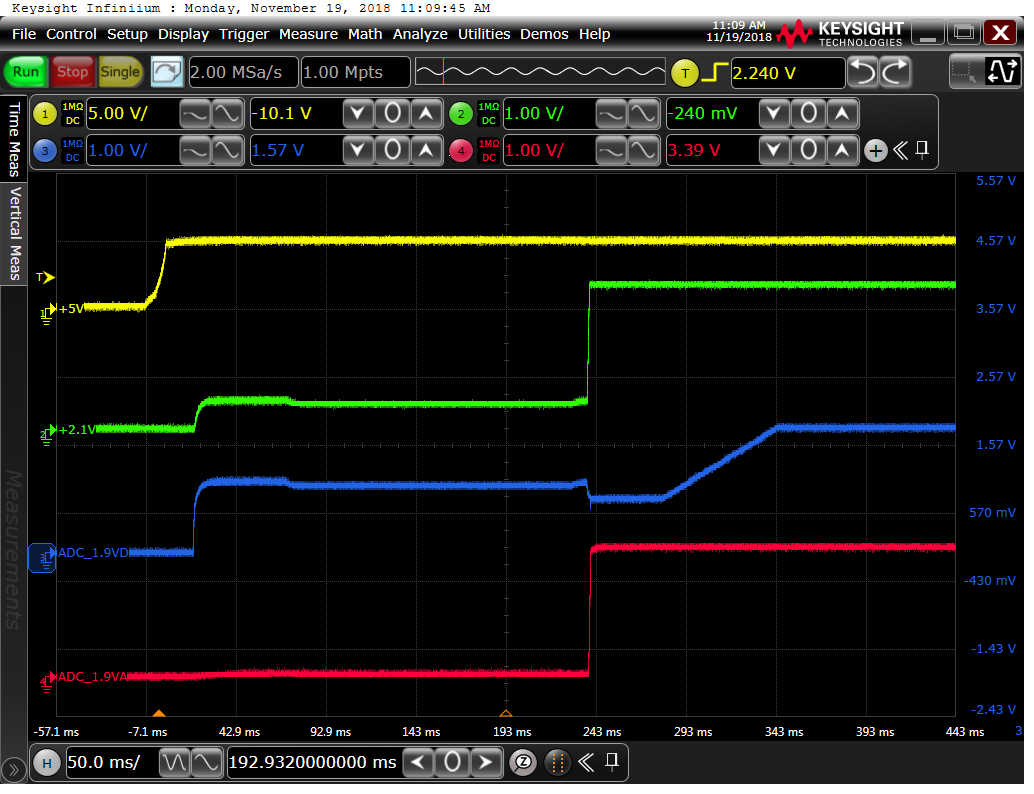

下面是浅蓝色屏幕截图顶部的数字信号的屏幕截图、它们驱动 FPGA 中每个 TPS7A8300上的 EN 引脚。 在屏幕截图底部测量了通道1、2、3和4的输出电压。

FPGA 脱离复位(n_rst)、然后在 LDO 上进行序列。 唯一的问题是、即使输出本应处于关闭状态、1.9VD 的输出端也存在大约800mV 的电压。

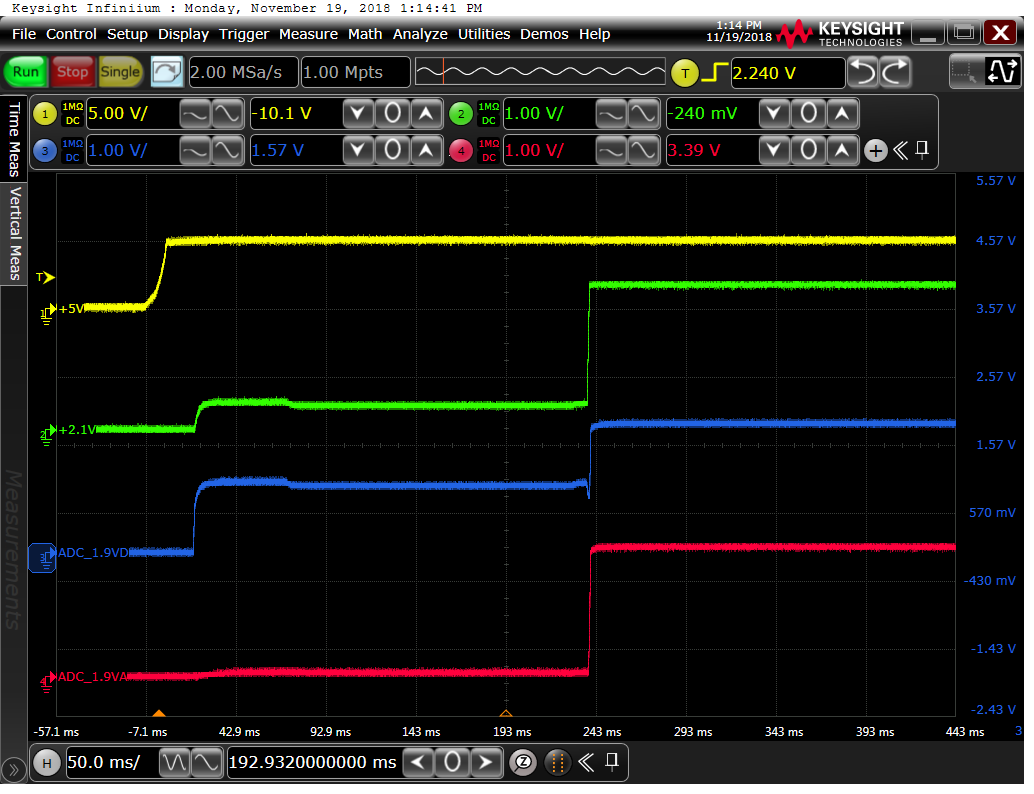

缩小后、您可以看到、当每个其他电源轨都处于零时、1.9VD 电源轨在加电时立即达到0.8V:

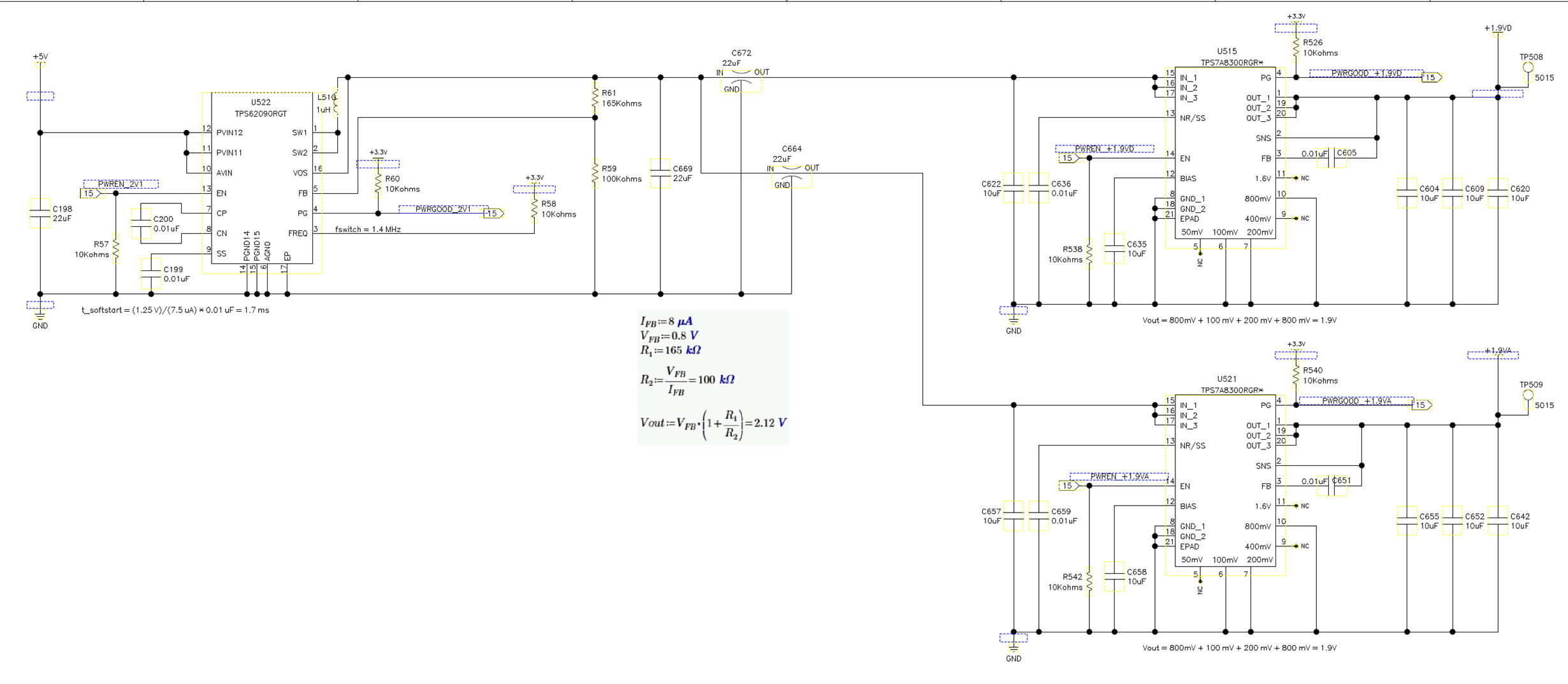

我的1.9VD 电路: