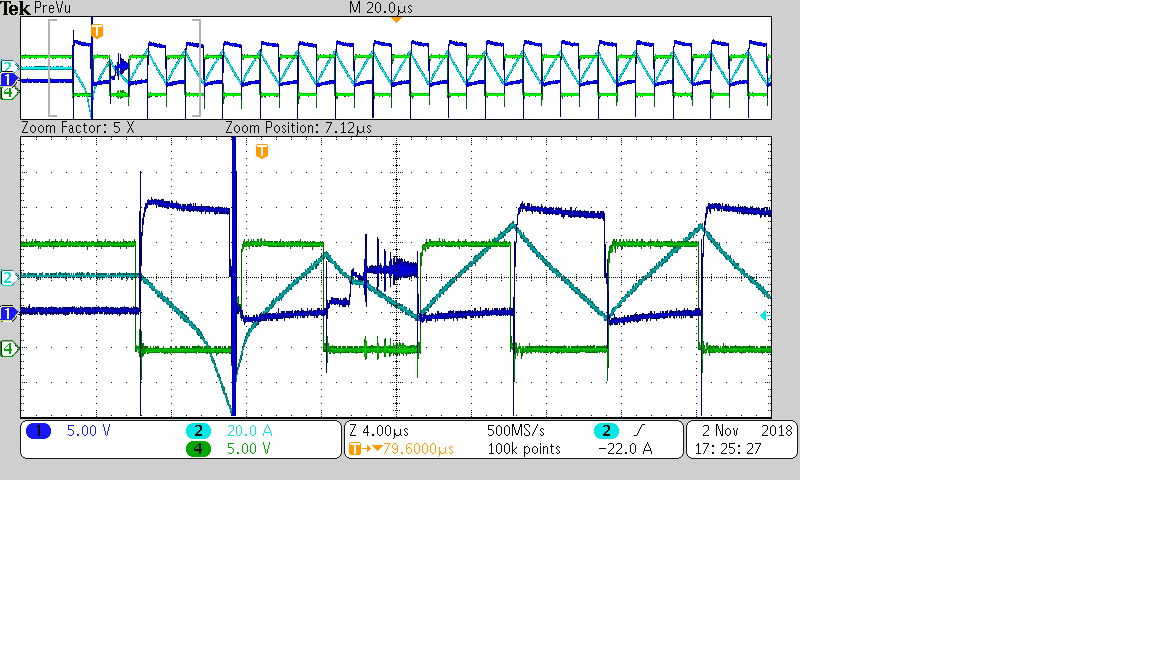

我使用其中的两 个驱动器来驱动双有源电桥转换器的一侧。 我在首次打开时在高侧输出中遇到毛刺脉冲。 我已经检查了 VDDA、它在15V 时稳定、具有较小的1/4V 至1/2V 突降。 启动期间会产生大量噪声、但我想知道这种行为的性质、以便尝试找到补丁。 启用驱动器之前、所有电源轨都已启动几秒钟。

INA/INB RC = 51欧姆+ 220pf

VDD1 = 3.3V、0.47uf 和0.01uf

使能引脚 RC = 51欧姆+ 220pf

CH1 (蓝色):高侧输出

CH2 (浅蓝色):电感器电流

CH4 (绿色):低侧输出