主题中讨论的其他器件: TPS54A20

大家好、

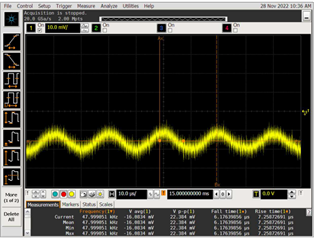

输出具有数十 kHz 的纹波。

12Vin 0.85Vout 设置。

该负载的电容总计为1300uF。

电容是否超出数据表建议值(1000uF)?

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Hirotsugu、

纹波频率是否恒定、不随负载变化?

低频振荡可能是不稳定的迹象。

但在不稳定的情况下、纹波频率不是很恒定、应随负载电流的变化或其他变化而变化。

实际上、1300 μ F 的陶瓷电容器超出了建议的值、可能会导致不稳定。

所有输出电容器(1300 uF)是否都是陶瓷型电容器?

如您所知、TPSM84A21内部已集成了电容器。

在大多数应用中、TPSM84A21 无需外部电容器或高达300uF 的外部陶瓷电容器即可使用。

如果 该纹波的频率相当恒定、我还会寻找可能直接耦合的外部频率、或通过生成"拍频"(freq1 - freq2)进行耦合的外部频率。

此致、

Yitzhak Bolurian

您好 Yitzhak、

发现所有器件都存在此问题。

我通过更改 EVM 上的 Cout 电容来验证了它。

Cout 没有周期性振荡、仅330uF、但使用多个100uF 时会发生周期性振荡。

附件仅显示100uF4 + 330uF 和330uF 的结果。

e2e.ti.com/.../TPSM84A21_5F00_Cout.pdf

这是该器件的特性吗?

周期性振荡是否处于不稳定状态?

此致、

Hirotsugu、您好!

感谢您提供此数据。

我已经仔细检查了这一点、实际上、这可能会在低输出电压和高输出电压下发生。

这不会导致无界不稳定性问题、因为环路频率高于纹波/低相位频率。

但无论如何、如果您想消除这种低频纹波、我们应该使用前馈电容器增加相位裕度。

您可以在 Vs+和 Vadj 引脚之间添加一个3.3nF 至4.7nF 的前馈电容器来解决此问题。

如果您决定尝试此操作、 请确保将 Vs+侧连接到尽可能靠近 IC 的位置。

此致、

Yitzhak Bolurian

您好 Yitzhak、

我尝试添加 CFF (4.7nF)。

它在小电流下得到了改进。

我将此 IC 用于 FPGA 的内核电源、但如果我按照 FPGA 的指导原则连接电容、它将以低频率振荡。

是否有任何方法可以防止振荡、同时保持指南的容量?

e2e.ti.com/.../TPSM84A21_5F00_Cout_2B00_Cff.pdf

此致、

您好 Yitzhak、

我在更改容量的 EVM 上进行了测试。

随着电容的增加、低频纹波也会增加。

即使该纹波在额定最大电容值(1000uF)范围内、该纹波也会发生吗?

e2e.ti.com/.../tpsm84a21_5F00_cout_12FF_.pdf

此致、

您好 Yitzhak、

我在没有额外 Cout 的情况下使用 EVM 测量了每个输出电压。

结果是否正确?

在相位裕度较小的频率下不会出现纹波。

Hirotsugu、您好!

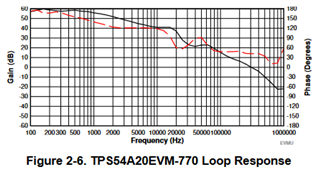

这是 TPS54A20 EVM 的波特图:

您可以注意 到、相位未降至15度以下。 越低、纹波越高、纹波就越有可能出现。

您所附的波形图、尤其是0.85V 波形图、在较低频率下似乎会受到测量噪声的影响、并且还会显示较低的相位骤降。

您可能需要使用"信号整形"来获得不同频率下不同级别的注入信号(如果您的网络分析器支持此功能)。

此致、

Yitzhak

您好 Yitzhak、

我使用信号整形测量了波特图。

当存在低频纹波时、增益为0dB、且不存在相位裕度。

此外、振荡频率看起来与 FCO 相同。

我认为这是一种震荡的症状、但请告诉我您的意见。

您好 Yitzhak、

我尝试添加 CFF、但相补角不会更高。

我认为 CFF 工作量更小、因为 Fzero 和 Fpole 接近于实现更低的输出电压。

我应该尝试更多的 CFF、还是有其他更正方法?

在 TPS54A20中、存在 R-C 校正。

e2e.ti.com/.../TPSM84A21_5F00_Cff.pdf

此致、

您好 Yitzhak、

我将测量环路响应、在 VS+和 Aadj 引脚之间增加 CFF。

如果在 VOUT 和 Vadj 引脚之间增加 CFF、我认为无法测量环路响应。

e2e.ti.com/.../TPSM84A21_5F00_how-to.pdf

此致、