Other Parts Discussed in Thread: TPS7A85, TPS7A85A, TPS7A83A, TIDA-01232

主题中讨论的其他器件: TPS7A83A、 TIDA-01232

大家好、我需要一些建议。

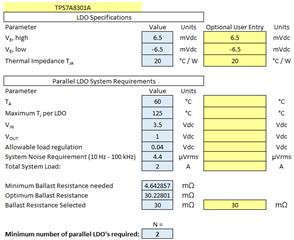

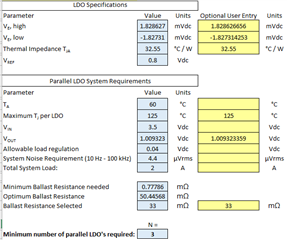

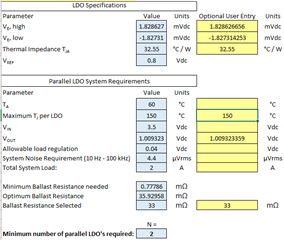

我必须使用 TPS7A85元件来满足以下参数:

输入电压:3.5V

输出电压:1V

输出电流:2A

允许的纹波:1mV

电压容差:3%

工作温度:高达60°C

使用 EN 和电源正常引脚

我无法使用直流/直流在 LDO 之前降低电压。

为了最大限度地提高电路的可靠性、该电路必须长时间(几年)持续运行、我想使用两个 TPS7A85。

串行设计很容易实现、但更容易出现故障。

相反、并行设计本质上更安全(即使是使用损坏的组件也能正常工作)、但实施起来更复杂。

您建议使用哪种解决方案?

提前感谢。

此致。