我昨天做了一些测试。 我对 ISO5451的 DESAT 保护机制有一些疑问。

现象:

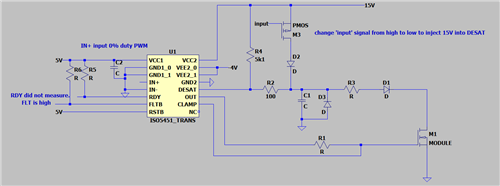

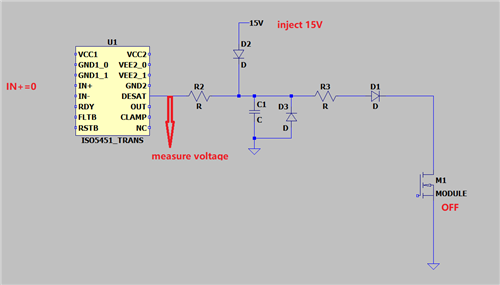

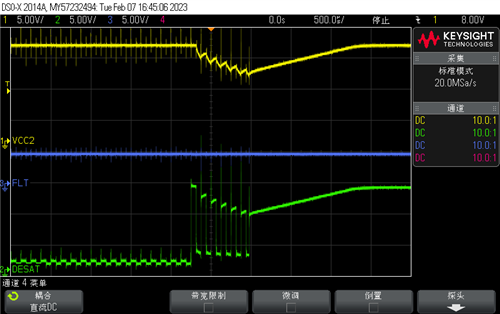

我强制 IN+为低电平、然后通过一个电阻器和一个二极管的外部电源向 DESAT 引脚注入15V 电压、测量 DESAT 引脚和 FLT 引脚的电压后、请参阅下图。 我注意到 DESAT 引脚 正在振动、FLT 引脚为高电平、请参阅下面的波形。

图表:

波形:

黄线为 VCC2;蓝线为 FLT;绿线为 DESAT。

问题:

这是不是说在电源模块关闭期间或输入+/OUT 为低电平、DESAT 功能处于非活动状态?

根据我的理解、DESAT 引脚具有内部 MOS、在电源模块关断期间、DESAT 引脚在内部通过开启内部 MOS 保持低电平、内部电流源关断、对吗?

您能否解释 DESAT 引脚的波形为何如此? 因为内部 MOS 的导通和关断?