请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

您好、ESE 会员:

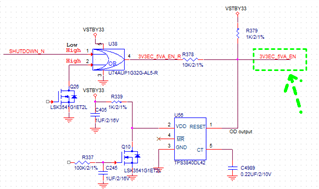

我们现在将 TPS3540DL 用于3.3V 电压监控器、但会遇到一些奇怪的症状:

根据 DS、输出引脚将在两种情况下置为有效(从高电平到低电平):

电压时的电压

VDD 降至负电压阈值(V IT-)以下

或者当手动复位(MR)被拉至低逻辑(V MR_L)时。

但在我的设计中、输出似乎始终为低电平、即 PIN2 (VDD)为高电平或低电平(我的#MR 引脚悬空)

您能提出可能的根本原因吗? 还是在原理图中避免了一些错误?

电源 Q10是一个 MOS AS 开关、它将 PIN2 VDD 拉至低电平以触发复位引脚为低电平脉冲、如果 Q10关闭、通常复位引脚应保持高电平、

但我们的问题是复位引脚将始终为低电平。

谢谢、

Steven