Thread 中讨论的其他器件: TPS65218EVM-100

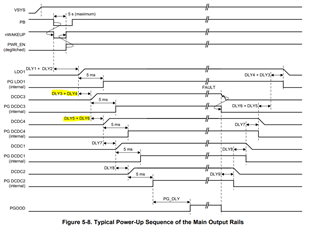

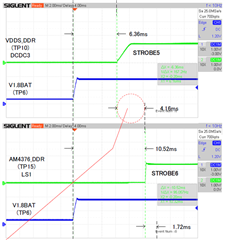

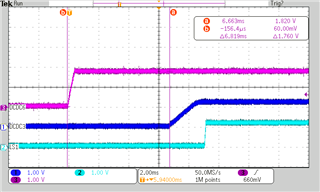

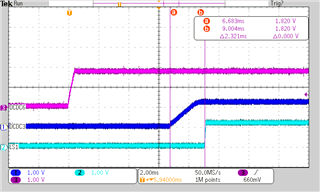

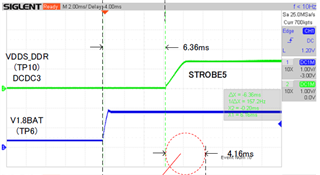

当从 TPS65218B1替换为 TPS65218D0而不更改电路和寄存器时、DCDC3序列存在差异。

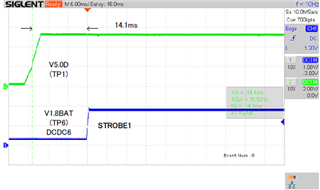

选通延迟设置保持默认值2ms。

TPS65218B1 (电流乘积)的延迟时间约为2.152ms、而 TPS65218D0的延迟时间约为4.16ms。

这是从 B1更改为 D0的改进吗?

或者是否有其他因素?

请参阅以下波形。

※V1.8BAT (TP6):DCDC6

作为参考、寄存器转储如下所示。

・TPS65218D0

0x00:05 10 00 00 00 28 00 00

0x08:00 00 00 00 00 00 00 00

0x10:00 3f 13 4c c0 00 19 29

0x18:92 b2 06 1f 00 00 00

0x20:00 98 75 12 63 03

・Ω TPS65218B1

0x00:03 10 00 00 00 28 00 00

0x08:00 00 00 00 00 00 00 00

0x10:00 3f 13 48 c0 00 19 29

0x18:92 b2 06 1f 00 00 00

0x20:00 98 75 12 63 03

此致、

聪