主题中讨论的其他器件: PMP11254

在正常电源下、LAN8740 IC 电路正常发热、但在 TPS23752 IC POE 上、LAN8740 IC 电源发热非常高。 请为这个做必要的准备。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

e2e.ti.com/.../POE_2D00_TI.pdf

请查找原理图。

此致、

帕拉夫

尊敬的 Diang:

感谢您的回复。

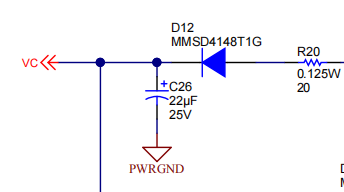

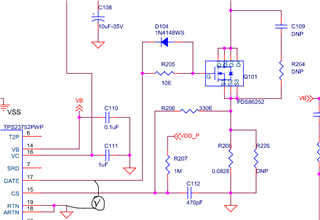

我在 Vc 上测量了54V-POE 输入、DSO-RTN 和12V-P。 请检查并提供建议。

1. 54V-POE

2. Vc - RTN

3.12V-P

我需要更多关于原理图的问题。

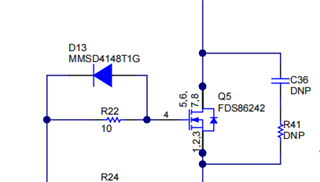

我们根据 PMP11254参考设计进行设计。 低于 D13二极管在栅极驱动中起什么作用?

我们的器件是气密 的所以 POE 区域的加热, PCB 的加热非常高。

关于上述问题、请帮助我。

期待您的参与!

此致、

帕拉夫

Pallav、您好!

感谢您的信息。

1. D13确保 Q5的快速关闭速度。 这有助于减少关闭能量。 如果您有一个次级侧同步 FET、这也有助于减少 pri-sec FET 击穿时间。

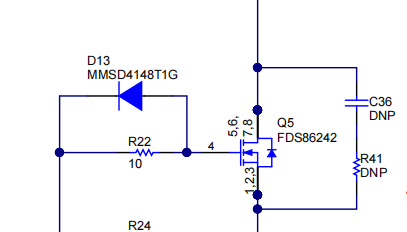

交换 D12和 R20位置应该没有问题。

3. 12V-P 电压具有1.68V 的峰峰值纹波。 想知道您是否有 LDO 到变压器12V-P 到3.3V 输入来提供 LAN8740A、 通常、LDO 应减轻 大部分纹波。

4. 对于输出纹波、看起来 VC 高于 UVLO、VDD 也稳定。 您能帮助测量 GATE -RTN 电压吗? 只是想知道栅极是否不连续 、从而导致12V-P 上出现较大纹波。

此致、

帝昂

Pallav、您好!

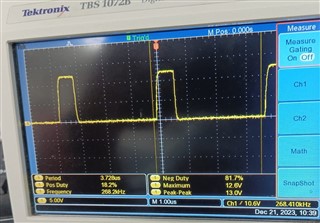

感谢栅极电压波形。 占空比(D)约为17%。 匝数比为2:1。

根据 N*Vout = D/(1-D)* Vin,Vin 为 ~117V, 高于54V-POE 输入。 看起来栅极占空比可能在相同负载电流下发生变化或负载太轻。 您可以帮助检查:

-一个缩小的栅极波形、用于查看占空比是否保持在~17%或者在同一负载电流下是可变的

- 如果在负载较重时 Vout 可以稳定。

此致、

帝昂

尊敬的 Diang:

我附上了 仅作为我们的器件加载时的栅极波形的照片、更改占空比12%- 16%

我附上了 加载时的栅极波形的照片、因为仅我们的器件和锁、改变占空比17%- 18%。

在某些 器件中 、从磁场恢复、这会导致 Vc 引脚损坏(显示导通性 或显示低阻抗)相关问题。

我们检查波形、发现波纹约为 1.2V 峰峰值、现在我们 通过在 Vc 引脚处添加4.7uF-50V 电容器将峰峰电压降低到440mV 到600mV。

此外 、我们 通过 添加47uF-50V 陶瓷电容器将输出电压12V-P 纹波降低至280mV。

我们还需要对这个问题采取什么保护措施。 当我们 在 Vc 引脚上添加12V 齐纳二极管会有所帮助吗?

我们将 LCB1608-221Y-N 用于 L14。 请查看附件数据表。 告诉我、它是否正常?

e2e.ti.com/.../Large-Current-Multilayer-Chip-Beads-for-LCB1608-_2800_1_2900_.pdf

Pallav、您好!

新年快乐!

对于 π 型滤波器中的电感值、通常电感器的较大电感和电容器中的较小杂散电感可以提高性能。 BLM18SG121TN1D 是0603封装类型、可能 不够大。 您可使用以下链接来帮助设计文件管理器: www.ti.com/.../SSZT824

J4的端子到整流器看起来很好。

此致、

帝昂