Thread 中讨论的其他器件: AM3352、TPS65218、 TPS6521815

尊敬的 TI 专家团队:

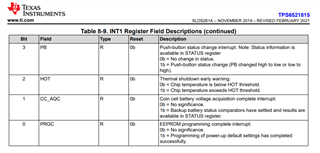

我写信的目的是希望澄清 TPS65216中 INT2寄存器的位0。

在数据表中、这个位被描述为一个"被保留"。

我们目前正在评估采用 AM3352和 TPS65216的定制设计电路板的工程原型。

我们还遇到了一个问题、即 Linux 无法在其中一个原型板上正确启动。

此问题的发生率大约为30%、电路板有时正常启动、有时则无法正常启动。

其他原型板均不会出现此问题、但我们需要确定此问题是由设计缺陷还是单个组件中的缺陷引起的。

我们注意到了成功引导尝试和不成功引导尝试之间 INT1和 INT2寄存器值的差异。 值如下所示。

引导成功:

INT1 = 1 0、 INT2 = 0 0

启动失败:

INT1 = 0 0、 INT2 = 0 1

我们知道 INT1寄存器的第4位与 AC_DET 状态相关、我们将在最后对此进行研究。

不过、您能否深入了解 INT2寄存器第0位的差异表示什么?

此外、即使在启动失败的情况下、DCDC1到 DCDC4以及 LDO1电源输出也能正常工作。

执行上电序列后、这些输出稳定地为 AM3352供电、这可以通过示波器波形得到确认。

如果您有任何建议或意见、我将不胜感激。

感谢您的支持。

此致、

井上太