您好~

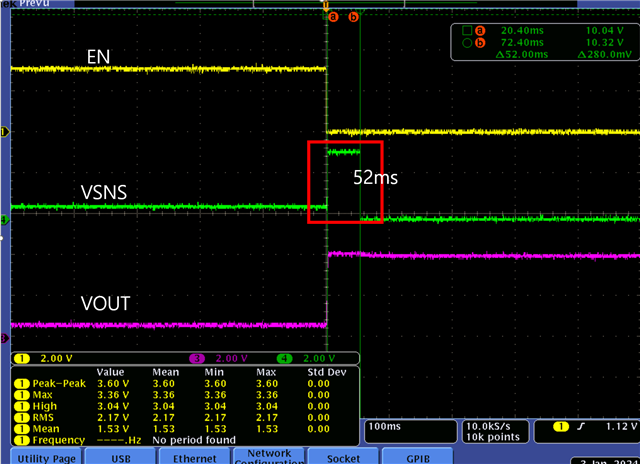

IN1=主电源(关闭状态、0V)、IN2=连接的 BATT。

如图所示、施加了 EN=LOW 和 VSNS = 52ms 高电平。

即使在 VSNS=HIGH (52ms)和 IN2 (BATT) 为输出期间、VOUT 也不会成为 IN1 (0V)。

当 VSNS =持续高电平时、确认输出变为0V。

VOUT 成为 IN1的 VSNS 最短时间是多少?

此致。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好~

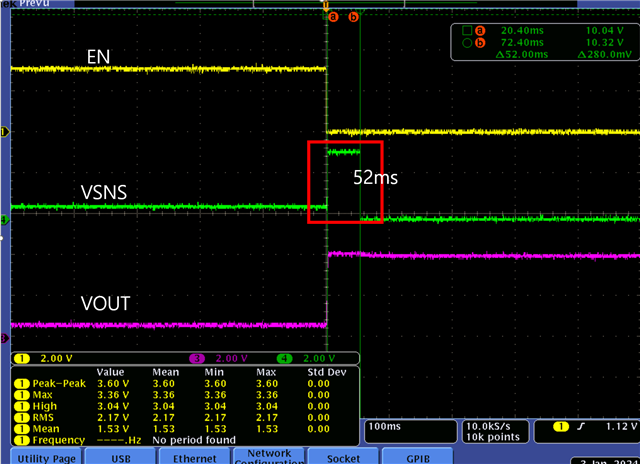

IN1=主电源(关闭状态、0V)、IN2=连接的 BATT。

如图所示、施加了 EN=LOW 和 VSNS = 52ms 高电平。

即使在 VSNS=HIGH (52ms)和 IN2 (BATT) 为输出期间、VOUT 也不会成为 IN1 (0V)。

当 VSNS =持续高电平时、确认输出变为0V。

VOUT 成为 IN1的 VSNS 最短时间是多少?

此致。

Patrick、您好!

观察上面的 VOUT 波形可知、起始电压为0V。 启用后、保持输出电压。

它由 TPS2113->BUCK-BOOST->LOAD (1A)组成。

如果保持了 VSNS、则可以像表格一样确认操作。

当 VSNS 的脉冲宽度为52m 时、输出为 IN2。

1. VSNS 是否有最低的维护时间?

2.无论脉冲宽度如何,它的操作是否应该像一个工作台一样?

3.如果 EN 和 VSNS 同时获得批准,是否有可能发生这种情况?

4.当 VSNS = N 时。 通常会产生大约1.6V 的电压。 原因是什么?

此致。

权

权赫

在数据表中、切换看起来在切换 VSNS 大约15us 后发生。 我想我们看到的并不是因为切换相对于 VSNS 会延迟。

2.是的,只要脉冲大于此~15us,它就应按照表操作。 但是、在引脚说明中、我看到只有当输入高于 UVLO 阈值(1.25V 下降、1.3V 上升)时、才能选择输入。 如果 VSNS > 0.8V 且 VIN1 < UVLO、OUT 应为 Hi-Z

3.是的、我认为这里发生的情况是、在 EN 变为低电平与器件看到 VSNS 为高电平的时间很短、因为 IN2与 OUT 相连接、从而在 VSNS 脉冲期间产生高电压。 我感兴趣的是、当该器件切换回 IN2时、VOUT 略有下降。 VSNS 脉冲期间的负载电流是多少?

此外、您能否测试 EN 变为低电平和 VSNS 变为高电平的间隔大于10ms (极大的延迟、以证明确切的想法)的相同情形? 这应该有助于回答我们的问题。

4.可能发生的情况是、当 VSNS 悬空时、器件会在 IN1和 IN2之间不断切换、因为没有定义的电平、器件会在切换中花费很大一部分时间、从而降低直流电压。

谢谢。

帕特里克

Patrick、您好!

感谢您的答复。

3. IN1或 IN2的负载电流相同(1A)。 电池连接到 IN2、因此由于电流消耗、电压几乎下降。

遗憾的是、我现在无法再做任何测试、所以下次我会做。 我将在下一次测试中再次询问该问题。

4.最后一个问题是不够的。 抱歉~~。

当 VSNS = N.C.时、会发生 VSNS = 1.6V。

在功能方框图中、它是比较器输入端口。 我不明白为什么会出现 VSNS = 1.6V。

谢谢。

权

权赫

3.好的,明白-请让我知道测试的结果,当你可以,希望它给我们一个清楚的情况。

4.啊,我的道歉,因为我误解了这个问题-我们通常会收到有关输入悬空时的输出行为的问题。

尽管我不确定、但我认为 VSNS 比较器使用 BJT 架构、这会将输入/VSNS BJT 的基极电压与 BJT 发射器的电压相同、后者会偏置。

您是否计划让 VSNS 有时浮动? 如果是、我建议在它上面放置一个弱上拉/下拉电阻器以实现冗余。

谢谢。

帕特里克