Other Parts Discussed in Thread: REF3430, REF54, DRV8316

主题中讨论的其他器件: REF5030、 REF54、 DRV8316

嗨、团队,

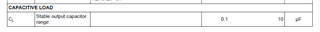

REF3430的 最大容性负载要求在数据表中为10uf。

该参数是如何生成的?

如果负载电容大于10uF (例如80uF)、会发生什么情况?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我已浏览了 TMS320F28P65x 技术参考、第18.14.6节包含此建议的外部参考电路:

您是否计划使用与此类似的电路设计? 如果是、那么在16位单端 ADC 的电压基准之后、CA 似乎为22µF (所有其他 ADC 似乎都需要一个2.2 µF 电容器)。 他们也似乎未使用隔离电阻器。

此外、您使用需要10 µF 电容器的 REF3430驱动的其他哪些芯片?

谢谢。

杰克逊

您好!

回到您原来关于 REF3430负载电容的问题、如果您使用的基准电路与 28P65技术基准中的电路类似、 如果要为 DRV8316使用0.1µF 电容器、在本应用中使用 REF3430应该不会有问题。

以下是我针对您的其他问题提出的建议:

1.

我的理解是电阻器 RA 提供 RISO 的功能。 我不确定我的理解是否正确。

我将遵循技术参考指南 18.14.6节中显示的配置、其中 RA 与 CA 串联。

2.

此外、 我能否使用一个运算放大器来驱动三个用于 DSP 的 ADC?

如 技术参考指南的第18.14.6节所述、 如果基准引脚共用一个运算放大器驱动器、性能会略有下降、但总的来说、这种类型的电路确实适用于通用 ADC。 我会邀请 对该器件有更深入了解的人 、就是否可以使用一个运算放大器来驱动所有三个 ADC 的基准发表评论。

谢谢。

杰克逊

Rui、您好、

不建议 在不同的模式下运行 ADC、其中一个作为16位运行、另两个作为12位运行。 这属于异步操作的范围、在异步操作中、转换噪声可能会耦合到 VREFLO 线路上。 请参阅 ADC 章节18.14.1 (确保异步运行)。 基本前提是所有 ADC 都应同时触发、所有 S/H 时间都相同、因此所有3个 ADC 的转换阶段都将同时发生。 12位和16位 ADC 时序不同、因此一个采用16位模式运行、而另两个采用12位模式、基本上会将转换操作置于异步模式。 异步工作模式会从转换阶段产生串扰、这足以降低 ADC 的性能。 这将是 VREFHI 配置拓扑的更大问题。

所有3个 ADC 都应该作为16位模式或12位模式运行。 这里唯一的例外是、如果16位模式 ADC 正在运行、那么2个 ADC 中的任何一个都不应进行转换、反之亦然。

此致、

约瑟夫