主题中讨论的其他器件:TPS62867

您好、TI。

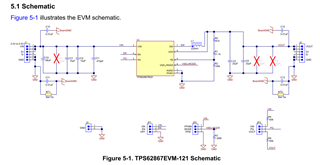

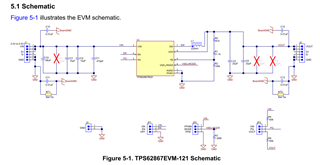

尝试使用 TPS62867进行 EVM 验证、如图1所示。

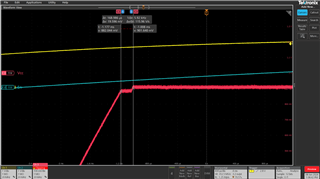

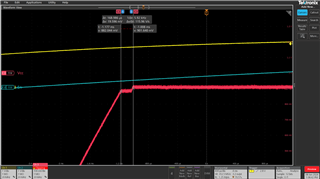

我发现 Vout 在上升到目标值之前存在间隙、 如图2所示

您能帮助解释一下这是正常情况吗?

感谢您的大力支持!!!

图1

图2

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、TI。

尝试使用 TPS62867进行 EVM 验证、如图1所示。

我发现 Vout 在上升到目标值之前存在间隙、 如图2所示

您能帮助解释一下这是正常情况吗?

感谢您的大力支持!!!

图1

图2

您好!

您能否说明一下、您保证时间是什么意思?

这取决于器件的负载电流。 根据我们拥有的数据、我可以观察到这种行为还取决于输出电压和负载电流。

还有一个应用手册详细介绍了启动行为:

https://www.ti.com/lit/an/slva866a/slva866a.pdf?ts = 1660735817891

请告诉我这是否有帮助。

谢谢。此

致、 斯内哈