主题中讨论的其他器件: DAC63204

根据反馈电阻器、我们设置输出电压、但在仿真(PSpice)中、我们注意到、如果输出电压超过1.2V、仿真会卡住并得出误差。 看起来不支持1.2V 的输出移动。 您能否检查并确认发生这种情况的原因?

墨辛

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Mohsin:

我将尝试通过将 Ref 电阻更改为更高的 Vout 来进行仿真、但是电路配置有点奇怪、似乎并不是一个常见的用例。

请问目的是甚么? 您是否尝试并联 LDO? 或者将一个 LDO 的 SNS 绑定到另一个 LDO 的输出有什么目的?

通过查看每个单独的 LDO、一个应提供1.8V 的 Vout、另一个应提供0.9V。 PSpice 可能会因以这种方式连接 LDO 而断开、因为 PSpice 不会以这种方式连接。

此致!

埃德加·阿科斯塔

尊敬的 Mohsin:

这些是我最后进行的相同设置。

您是否尝试过单独运行单个器件?

我可以问什么是意向吗? 您是否尝试并联 LDO? 或者将一个 LDO 的 SNS 绑定到另一个 LDO 的输出有什么目的? [/报价]同样、如果目的是并联 LDO、则配置不同。

我也强烈建议查看: TPS7A57EVM-081评估板| TI.com

和通读: 可扩展、高电流、低噪声并行 LDO 参考设计(TI.com)

此致!

埃德加·阿科斯塔

尊敬的 Mohsin:

您使用什么是 Rref 值来获得更高的输出电压? 我建议尝试使用 Vin 和 Vbias 的两个不同来源。

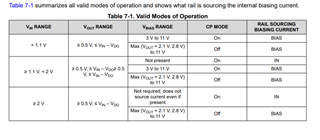

确保 Vbias 设置正确。 该器件具有数据表中列出的以下表格:

建议将 Vbias 至少设置为比 Vout 高3.2V、因此、Vbias = Vout+3.2。

模型的功能设置为尽可能接近表7-1。 如果没有电荷泵电压、则 Vbias 必须高于3V。

该模型还会检查 BIAS 是否高于 Vout+2.1V、但建议使用高于2.1V 的值。

此致!

埃德加·阿科斯塔

您好!

感谢您提供的信息。

是的、最好使用一个电阻器。 特别是在 LDO 将在 DAC 之前开启的情况下。 在稳态期间、应该不会出现任何问题、但 NR/SS 和 REF 之间有一个内部开关、此开关会根据 Vref 的条件闭合、因此、为了防止出现任何意外/异常行为、建议安装 Rref。

从 LDO 的角度来看、基准电压上的3.3V 仍然可以接受、因为建议的最大电压为5.3V。

就数据表中讨论的应用而言、它是一个示例、展示了裕量是可以实现的、并且根据应用、%可以变化。

由于内部电流源用于设置 Vref、并且知道电压裕量和调节是 DAC63204的主要应用、因此选择并首选电流 DAC +灌电流/拉电流功能、因为仅仅通过更改代码来更改电流更轻松且方便。

此致!

埃德加·阿科斯塔