您好、TI 工程师!

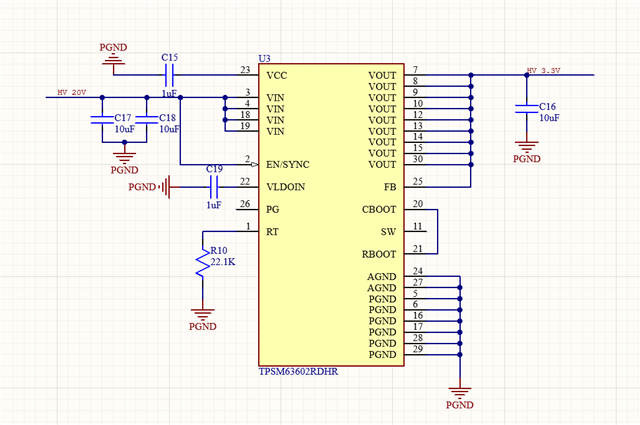

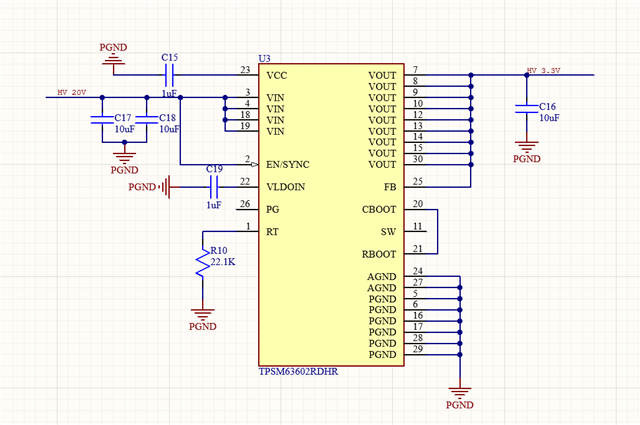

我在测试 TPSM63602V3时遇到问题。 我观察到、即使在空载条件下、一半的 IC 也会出现明显的温度升高。 我已经将原理图、热分布、PCB 布局和照片附加到了这个线程上。 您能仔细看一下设计并提供您的见解或建议吗? 谢谢!

注意:FL1是共模扼流圈、当它被去除时、3.3V 电源无负载。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、TI 工程师!

我在测试 TPSM63602V3时遇到问题。 我观察到、即使在空载条件下、一半的 IC 也会出现明显的温度升高。 我已经将原理图、热分布、PCB 布局和照片附加到了这个线程上。 您能仔细看一下设计并提供您的见解或建议吗? 谢谢!

注意:FL1是共模扼流圈、当它被去除时、3.3V 电源无负载。

尊敬的 Liyang:

如上所示布局上的接地平面非常小。 为接地平面设置合适大小的覆铜区对于帮助 IC 散热非常重要。 以下是热设计应用手册和数据表中的示例布局: https://www.ti.com/lit/an/snva951/snva951.pdf

您是否可以共享 PCB 的其他层?

此致、

岭